# PY32F031 Series

## 32-bit ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ Microcontroller

# **Reference Manual**

Puya Semiconductor (Shanghai) Co., Ltd.

## Contents

| 1. | List | t of a | bbreviations for registers                | 19 |

|----|------|--------|-------------------------------------------|----|

| 2. | Sys  | stem   | architecture                              | 20 |

| 3. | Me   | mory   | and bus architecture                      | 21 |

|    | 3.1. | Syst   | tem architecture                          | 21 |

|    | 3.2. | Men    | nory organization                         | 22 |

|    | 3.3. | Emb    | bedded SRAM                               | 25 |

|    | 3.4. | Flas   | h memory                                  | 25 |

|    | 3.5. | Boo    | t modes                                   | 25 |

|    | 3.5. | .1.    | Memory physical mapping                   |    |

|    | 3.5. |        | Embedded bootstrapper                     | 26 |

| 4. | Em   |        | ed Flash memory                           |    |

|    | 4.1. | Mair   | n features of flash memory                | 27 |

|    | 4.2. | Flas   | h memory functional description           |    |

|    | 4.2. | .1.    | Flash memory organization                 |    |

|    | 4.2. | .2.    | Flash read operation and access latency   | 27 |

|    | 4.2. |        | Flash program and erase operations        |    |

|    | 4.3. |        | que device ID (UID)                       |    |

|    | 4.4. | FLA    | SH option bytes                           |    |

|    | 4.4. | .1.    | Flash option byte description             |    |

|    | 4.4. |        | FLASH option bytes                        |    |

|    | 4.5. | Flas   | h option bytes                            |    |

|    | 4.5. | .1.    | HSI_TRIMMING_FOR_USER                     | 38 |

|    | 4.5. | .2.    | HSI_4M/8M/16M/22.12M/24M_EPPARA0          | 38 |

|    | 4.5. | .3.    | HSI_4M/8M/16M/22.12M/24M_EPPARA1          | 38 |

|    | 4.5. | .4.    | HSI_4M/8M/16M/22.12M/24M_EPPARA2          | 39 |

|    | 4.5. | .5.    | HSI_4M/8M/16M/22.12M/24M_EPPARA3          | 39 |

|    | 4.5. | .6.    | HSI_4M/8M/16M/22.12M/24M_EPPARA4          | 39 |

|    | 4.5. | .7.    | Flash User Data Bytes                     | 39 |

|    | 4.6. | Flas   | h protection                              | 40 |

|    | 4.6. | .1.    | SDK area protection                       | 41 |

|    | 4.6. | .2.    | Flash memory read protection              | 41 |

|    | 4.6. | .3.    | Flash write protection                    | 42 |

|    | 4.6. | .4.    | Option byte write protection              | 43 |

|    | 4.7. | Flas   | h interrupt                               | 43 |

|    | 4.8. | Flas   | h registers                               | 43 |

|    | 4.8. | .1.    | FLASH access control register (FLASH_ACR) | 43 |

|    | 4.8. | .2.    | FLASH key register (FLASH_KEYR)           | 44 |

|    | 4.8. | .3.    | FLASH option key register (FLASH_OPTKEYR) | 44 |

|    | 4.8. | .4.    | FLASH status register (FLASH_SR)          | 44 |

|    | 4.8.5.   | FLASH control register (FLASH_CR)                                     | 45 |

|----|----------|-----------------------------------------------------------------------|----|

|    | 4.8.6.   | FLASH option register (FLASH_OPTR)                                    | 47 |

|    | 4.8.7.   | FLASH SDK address register (FLASH_SDKR)                               | 48 |

|    | 4.8.8.   | FLASH WRP address register (FLASH_WRPR)                               | 48 |

|    | 4.8.9.   | FLASH sleep time configuration register (FLASH _ STCR)                | 49 |

|    | 4.8.10.  | FLASH TS0 register (FLASH_TS0)                                        | 50 |

|    | 4.8.11.  | FLASH TS1 register (FLASH_TS1)                                        | 50 |

|    | 4.8.12.  | FLASH TS2P register (FLASH_TS2P)                                      | 51 |

|    | 4.8.13.  | FLASH TPS3 register (FLASH_TPS3)                                      | 51 |

|    | 4.8.14.  | FLASH TS3 register (FLASH_TS3)                                        | 51 |

|    | 4.8.15.  | Flash page erase TPE register (Flash _ PERTPE)                        | 52 |

|    | 4.8.16.  | FLASH sector/mass erase tpe register (FLASH_SMERTPE)                  | 52 |

|    | 4.8.17.  | FLASH program TPE register (FLASH_PRGTPE)                             |    |

|    | 4.8.18.  | FLASH pre-program TPE register (FLASH_PRETPE)                         |    |

| 5. |          | control                                                               |    |

|    | 5.1. Pov | ver supply                                                            |    |

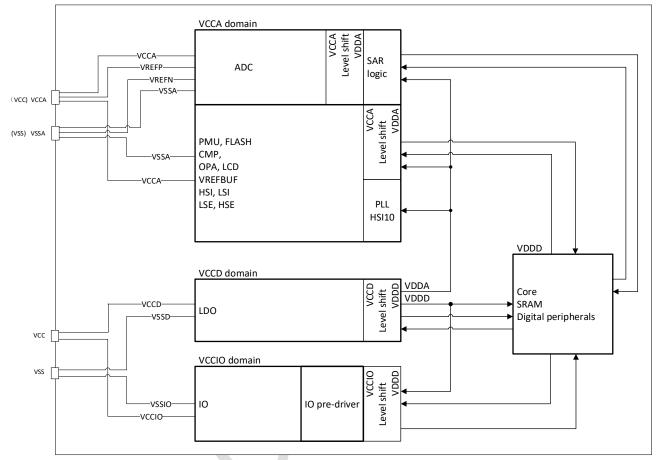

|    | 5.1.1.   | Power supply overview                                                 |    |

|    | 5.2. Vol | tage regulator                                                        | 54 |

|    | -        | namic voltage scaling management                                      |    |

|    | 5.4. Pov | ver monitoring                                                        | 56 |

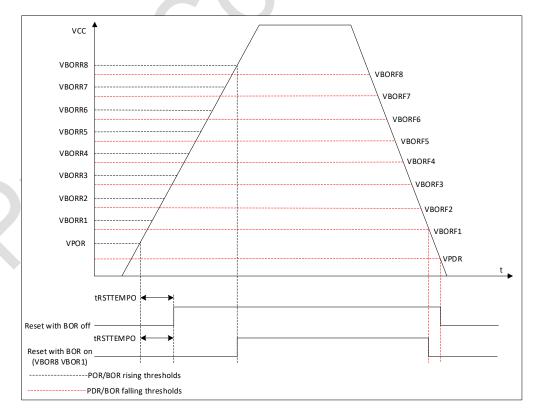

|    | 5.4.1.   | Power-on reset (POR) / power-down reset (PDR) / brown-out reset (BOR) |    |

| 6. |          | wer control                                                           |    |

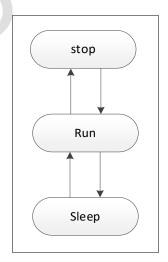

|    | 6.1. Lov | v-power modes                                                         |    |

|    | 6.1.1.   | Introduction                                                          |    |

|    | 6.1.2.   | Functionalities depending on the working mode                         | 58 |

|    | 6.2. Sle | ep mode                                                               |    |

|    | 6.2.1.   | Enter Sleep mode                                                      |    |

|    | 6.2.2.   | Exit Sleep mode                                                       | 59 |

|    | 6.3. Sto | p mode                                                                | 60 |

|    | 6.3.1.   | Enter Stop mode                                                       | 60 |

|    | 6.3.2.   | Exit Stop mode                                                        | 60 |

|    | 6.4. Red | duce the system clock frequency                                       | 61 |

|    |          | ipheral clock gating                                                  |    |

|    | 6.6. Pov | ver control registers                                                 |    |

|    | 6.6.1.   | Power control register 1 (PWR_CR1)                                    |    |

|    | 6.6.2.   | Power control register 2 (PWR_CR2)                                    |    |

|    | 6.6.3.   | PWR status register (PWR _ SR)                                        |    |

| 7. |          |                                                                       |    |

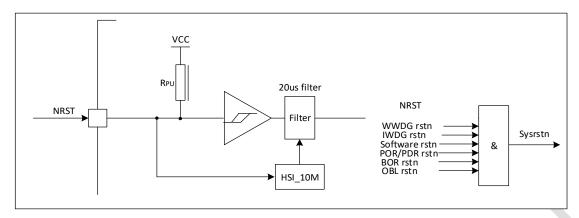

|    | 7.1. Res | set source                                                            |    |

|    | 7.1.1.   | Power reset                                                           | 64 |

|    | 7.1.2.    | System reset                                                      | .64 |

|----|-----------|-------------------------------------------------------------------|-----|

|    | 7.1.3.    | NRST pin (external reset)                                         | .64 |

|    | 7.1.4.    | Watchdog reset                                                    | .65 |

|    | 7.1.5.    | Software reset                                                    | .65 |

|    | 7.1.6.    | Option byte reload reset                                          | .65 |

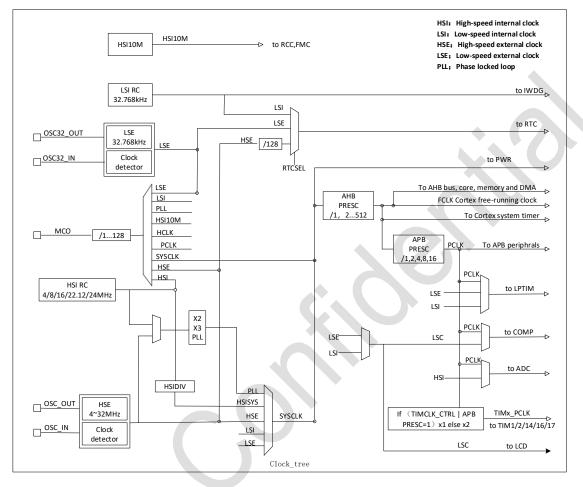

| 8. | Clocks    |                                                                   | .66 |

| 8  | 3.1. Cloc | k sources                                                         | .66 |

|    | 8.1.1.    | External high speed clock HSE                                     | .66 |

|    | 8.1.2.    | External low speed clock LSE                                      | .66 |

|    | 8.1.3.    | Internal high-speed clock HSI                                     |     |

|    | 8.1.4.    | HIS_10M                                                           |     |

|    | 8.1.5.    | Internal low speed clock LSI                                      | .66 |

|    | 8.1.6.    | PLL                                                               |     |

| 8  |           | sk tree                                                           |     |

| 8  | 3.3. Cloc | x security system (CSS)                                           |     |

|    | 8.3.1.    | HSE _ CSS                                                         |     |

|    | 8.3.2.    | LSE _ CSS                                                         |     |

| 8  | 3.4. Outj | out clock capability                                              | .68 |

| 8  | 3.5. TIM  | 14 internal and external clock calibration                        | .68 |

|    | 8.5.1.    | HSI calibration                                                   |     |

|    | 8.5.2.    | LSI Calibration                                                   |     |

| 8  | 3.6. Res  | et/clock register                                                 | .70 |

|    | 8.6.1.    | Clock control register (RCC _ CR)                                 | .70 |

|    | 8.6.2.    | Internal clock source calibration register (RCC _ ICSCR)          | .72 |

|    | 8.6.3.    | Clock configuration register (RCC_CFGR)                           | .72 |

|    | 8.6.4.    | PLL configuration register (RCC _ PLLCFGR)                        | .74 |

|    | 8.6.5.    | External clock source control register (RCC _ ECSCR)              | .74 |

|    | 8.6.6.    | Clock interrupt enable register (RCC _ CIER)                      | .75 |

|    | 8.6.7.    | Clock interrupt flag register (RCC _ CIFR)                        | .75 |

|    | 8.6.8.    | Clock interrupt clear register (RCC _ CICR)                       | .76 |

|    | 8.6.9.    | I/O interface reset register (RCC _ IOPRSTR)                      | .77 |

|    | 8.6.10.   | AHB peripheral reset register (RCC _ AHBRSTR)                     | .77 |

|    | 8.6.11.   | APB peripheral reset register 1 (RCC _ APBRSTR1)                  | .78 |

|    | 8.6.12.   | APB peripheral reset register 2 (RCC _ APBRSTR2)                  | .79 |

|    | 8.6.13.   | I/O interface clock enable register (RCC _ IOPENR)                | .80 |

|    | 8.6.14.   | AHB peripheral clock enable register (RCC _ AHBENR)               | .80 |

|    | 8.6.15.   | APB peripheral clock enable register 1 (RCC _ APBENR1)            | .81 |

|    | 8.6.16.   | APB peripheral clock enable register 2 (RCC _ APBENR2)            | .82 |

|    | 8.6.17.   | Peripheral independent clock configuration register (RCC _ CCIPR) | .83 |

|    | 8.6.18.   | RCC domain control register (RCC _ BDCR)                          | .83 |

|     | 8.6. | 19.   | Control/status register (RCC_CSR)                                  | 84  |

|-----|------|-------|--------------------------------------------------------------------|-----|

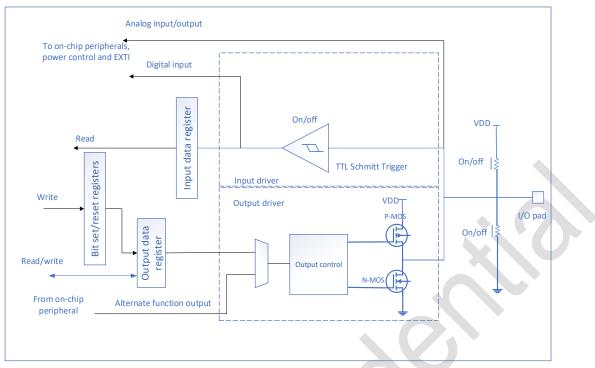

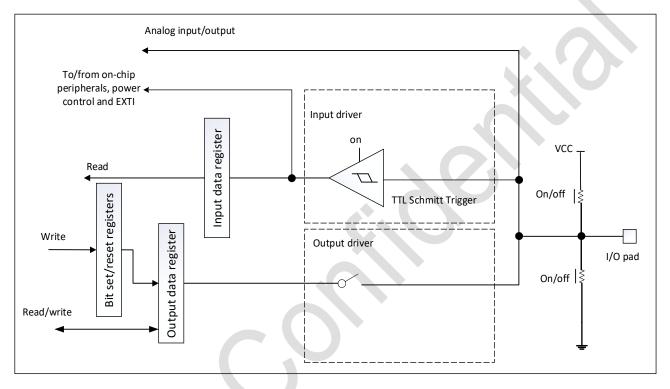

| 9.  | Ger  | neral | -purpose I/Os (GPIO)                                               | 86  |

| g   | ).1. | Intro | oduction                                                           | 86  |

| g   | ).2. | GPI   | O main features                                                    | 86  |

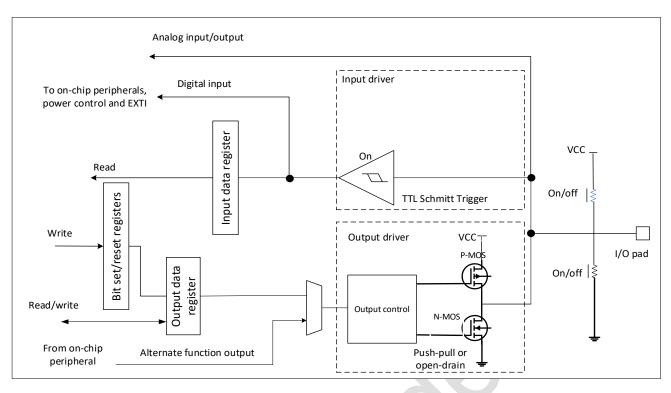

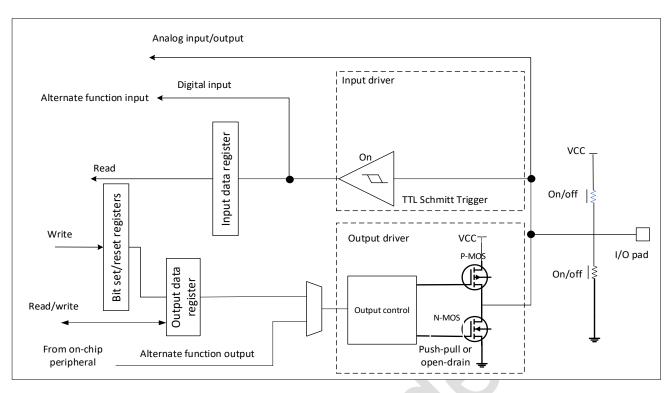

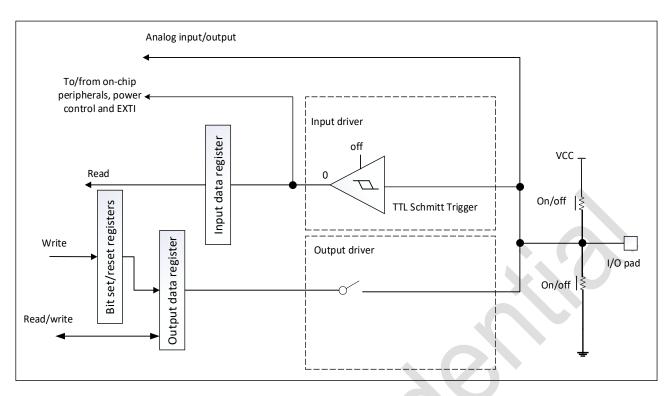

| g   | .3.  | GPI   | O functional description                                           | 86  |

|     | 9.3. | 1.    | General-purpose I/Os (GPIO)                                        | 87  |

|     | 9.3. | 2.    | I/O pin alternate function multiplexer and mapping                 | 87  |

|     | 9.3. | 3.    | I/O port control registers                                         |     |

|     | 9.3. | 4.    | I/O port data registers                                            |     |

|     | 9.3. | 5.    | I/O data bitwise handling                                          |     |

|     | 9.3. | 6.    | GPIO locking mechanism                                             |     |

|     | 9.3. | 7.    | I/O alternate function input/output                                |     |

|     | 9.3. | 8.    | External interrupt/wakeup lines                                    |     |

|     | 9.3. | 9.    | Input configuration                                                |     |

|     | 9.3. | 10.   | Output configuration                                               |     |

|     | 9.3. | 11.   | Alternate function configuration                                   |     |

|     | 9.3. | 12.   | Analog configuration                                               |     |

|     | 9.3. |       | Use LSE or HSE pins as GPIO                                        |     |

| g   | .4.  | GPI   | O registers                                                        | 93  |

|     | 9.4. | 1.    | GPIO port mode register (GPIOx _ MODER) (x = A, B, F)              | 93  |

|     | 9.4. | 2.    | GPIO port output type register (GPIOx _ OTYPER) (x = A, B, F)      | 94  |

|     | 9.4. | 3.    | GPIO port output speed register (GPIOx _ OSPEEDR) (x = A, B, F)    | 94  |

|     | 9.4. | 4.    | GPIO port pull-up/pull-down register (GPIOx _ PUPDR) (x = A, B, F) | 94  |

|     | 9.4. | 5.    | GPIO port input data register (GPIOx _ IDR) (x = A, B, F)          | 95  |

|     | 9.4. | 6.    | GPIO port output data register (GPIOx _ ODR) (x = A, B, F)         | 95  |

|     | 9.4. | 7.    | GPIO port bit set/reset register (GPIOx _ BSRR) (x = A, B, F)      | 95  |

|     | 9.4. | 8.    | GPIO port configuration lock register (GPIOx_LCKR) (x = A, B, F)   | 96  |

|     | 9.4. | 9.    | GPIO alternate function low register (GPIOx_AFRL) (x = A, B, F)    | 96  |

|     | 9.4. | 10.   | GPIO alternate function high register (GPIOx_AFRH) (x = A, B, F)   | 97  |

|     | 9.4. | 11.   | GPIO port bit reset register (GPIOx _ BRR) (x = A, B, F)           | 97  |

| 10. | S    | yste  | m configuration controller (SYSCFG)                                | 99  |

| 1   | 0.1. | S     | YSCFG registers                                                    | 99  |

|     | 10.1 | 1.1.  | SYSCFG configuration register 1 (SYSCFG_CFGR1)                     | 99  |

|     | 10.1 | 1.2.  | SYSCFG configuration register 2 (SYSCFG_CFGR2)                     | 100 |

|     | 10.1 | 1.3.  | SYSCFG configuration register 3 (SYSCFG_CFGR3)                     | 101 |

|     | 10.1 | 1.4.  | GPIOA filter enable register (PA _ ENS)                            |     |

|     | 10.1 | 1.5.  | GPIOB filter enable register (PB _ ENS)                            | 104 |

|     | 10.1 | 1.6.  | GPIOF filter enable register (PF _ ENS)                            |     |

|     | 10.1 | 1.7.  | I2C type IO configuration register (SYSCFG _ IOCFG)                | 104 |

|     | 10.1 | 1.8.  | GPIOA analog 2 enable register (PA _ ANA2EN)                       | 105 |

| 10.1.9   | <ol> <li>GPIOB analog 2 enable register (PB _ ANA2EN)</li> </ol> | 105 |

|----------|------------------------------------------------------------------|-----|

| 10.1.1   | 0. GPIOF analog 2 enable register (PF _ ANA2EN)                  |     |

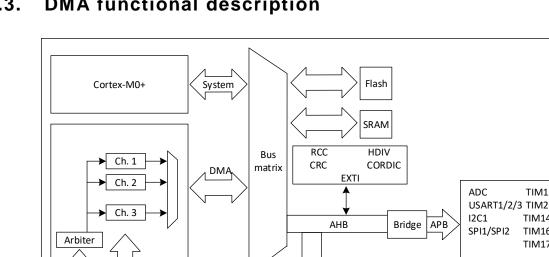

| 11. DM   | Α                                                                |     |

| 11.1.    | Introduction                                                     |     |

| 11.2.    | Main features                                                    |     |

| 11.3.    | DMA functional description                                       |     |

| 11.3.1   | . DMA transmission                                               |     |

| 11.3.2   | 2. Arbiter                                                       |     |

| 11.3.3   | B. DMA channel                                                   |     |

| 11.3.4   | 0                                                                |     |

| 11.3.5   | Ŭ                                                                |     |

| 11.3.6   | 6. DMA interrupts                                                |     |

| 11.3.7   |                                                                  |     |

| 11.4.    | DMA registers                                                    |     |

| 11.4.1   | . DMA interrupt status register (DMA_ISR)                        |     |

| 11.4.2   |                                                                  |     |

| 11.4.3   | B. DMA channel 1 configuration register (DMA _ CCRx)             | 115 |

| 11.4.4   | . DMA channel 1 data transfer quantity register (DMA _ CNDTRx)   | 116 |

| 11.4.5   | 5. DMA channel 1 peripheral address register (DMA _ CPAR1)       | 116 |

| 11.4.6   | 5. DMA channel 1 memory address register (DMA _ CMARx)           | 117 |

| 12. Inte | errupts and events                                               |     |

| 12.1.    | Nested vectored interrupt controller (NVIC)                      | 118 |

| 12.1.1   | . Main features                                                  | 118 |

| 12.1.2   | 2. SysTick calibration value register                            | 118 |

| 12.1.3   | B. Interrupt and exception vectors                               | 118 |

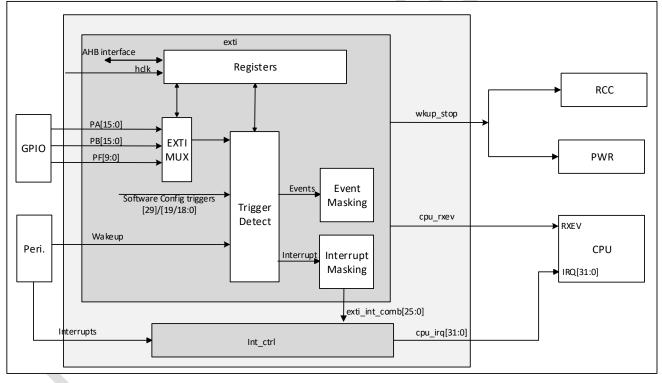

| 12.2.    | Extended interrupts and events controller (EXTI)                 | 119 |

| 12.2.1   | . EXTI main features                                             |     |

| 12.2.2   | 2. EXTI block diagram                                            |     |

| 12.2.3   | 8. EXTI connections between peripherals and CPU                  |     |

| 12.2.4   | EXTI configurable event trigger wake-up                          |     |

| 12.2.5   | EXTI direct event input wake-up                                  | 121 |

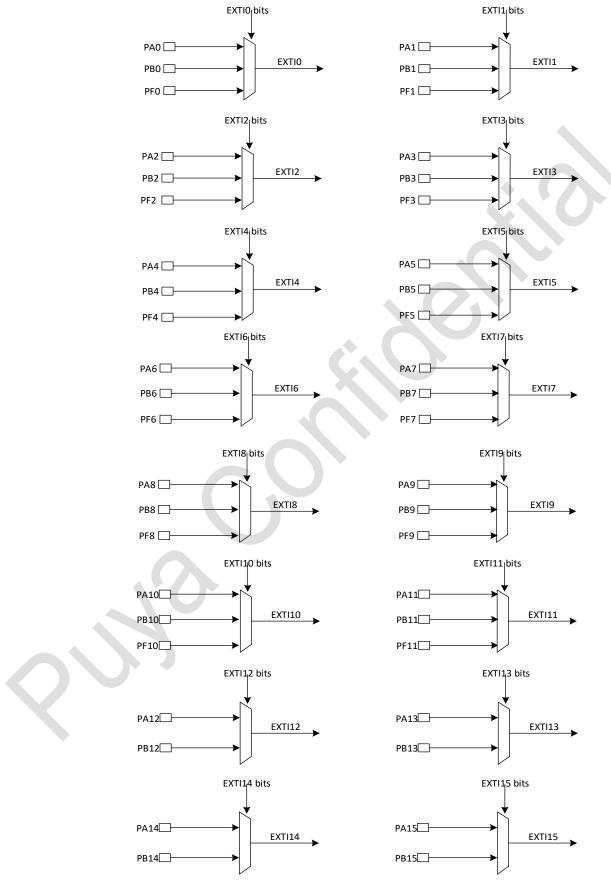

| 12.2.6   | EXTI multiplexer                                                 |     |

| 12.3.    | EXTI register                                                    |     |

| 12.3.1   | . EXTI rising trigger selection register (EXTI_RTSR)             |     |

| 12.3.2   | 2. EXTI falling trigger selection register (EXTI_FTSR)           |     |

| 12.3.3   | 8. Software interrupt event register (EXTI_SWIER)                | 126 |

| 12.3.4   | . Pending register (EXTI _ PR)                                   | 127 |

| 12.3.5   | EXTI external interrupt selection register 1 (EXTI_EXTICR1)      | 129 |

| 12.3.6   | EXTI external interrupt selection register 2 (EXTI_EXTICR2)      | 130 |

| 12.3.7   | . EXTI external interrupt selection register 3 (EXTI_EXTICR3)    |     |

|     | 12.3.8.             | EXTI external interrupt selection register 3 (EXTI_EXTICR3)         | 131 |

|-----|---------------------|---------------------------------------------------------------------|-----|

|     | 12.3.9.             | . Interrupt mask register (EXTI _ IMR)                              | 131 |

|     | 12.3.10             | 0. Event mask register (EXTI_EMR)                                   | 133 |

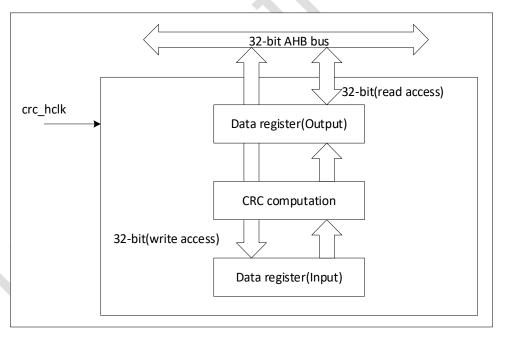

| 13. | Сус                 | lic redundancy check calculation unit (CRC)                         | 135 |

| 1   | 3.1.                | Introduction                                                        | 135 |

| 1   | 3.2.                | CRC main features                                                   | 135 |

| 1   | 3.3.                | CRC functional description                                          | 135 |

|     | 13.3.1.             | CRC block diagram                                                   | 135 |

| 1   | 3.4.                | CRC registers                                                       |     |

|     | 13.4.1.             |                                                                     | 136 |

|     | 13.4.2.             | 1 5 ( = )                                                           |     |

|     | 13.4.3.             | 3 ( _ /                                                             |     |

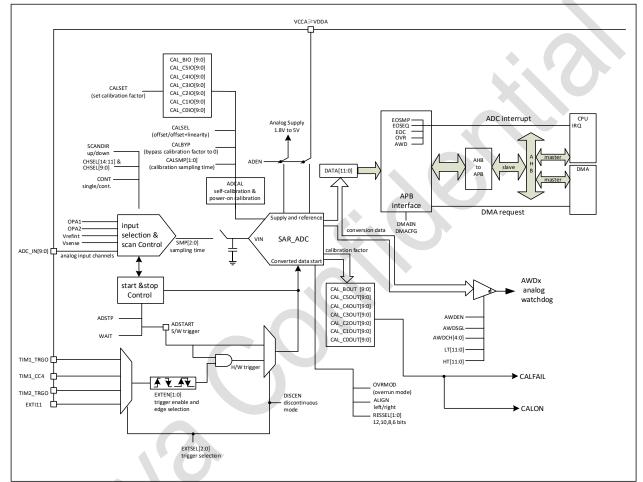

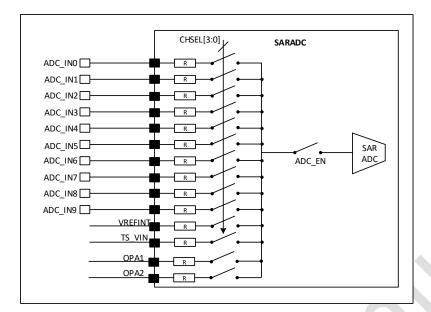

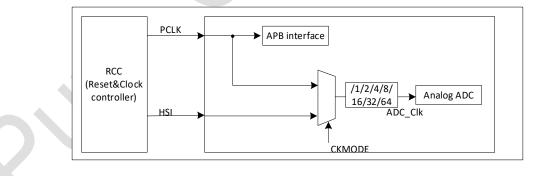

| 14. | Ana                 | log-to-digital converters (ADC)                                     |     |

| 1   | 4.1.                | Introduction                                                        |     |

| 1   | 4.2.                | ADC main features                                                   |     |

| 1   | 4.3.                | ADC functional descriptionADC functional description                |     |

|     | 14.3.1.             | 5                                                                   |     |

|     | 14.3.2.             |                                                                     |     |

|     | 14.3.3.             |                                                                     |     |

|     | 14.3.4.             |                                                                     |     |

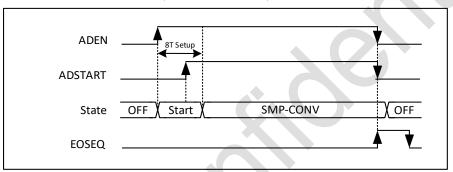

|     | 14.3.5.             | Configuring the ADC                                                 | 141 |

|     | 14.3.6.             |                                                                     |     |

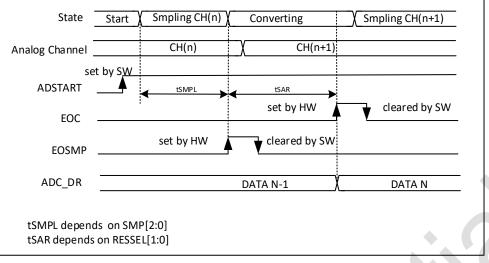

|     | 14.3.7.             | Programmable sampling time (SMP)                                    | 142 |

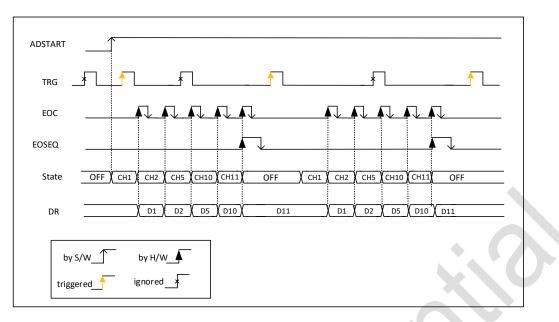

|     | 14.3.8.             | Single conversion mode (CONT = 0, DISCEN = 0)                       | 142 |

|     | 14.3.9.             | Continuous conversion mode (CONT=1)                                 | 143 |

|     | 14.3.10             | 0. Discontinuous conversion mode (DISCEN = 1)                       | 143 |

|     | 14.3.1 <sup>-</sup> | 1. Starting conversions (ADSTART)                                   | 144 |

|     | 14.3.12             | 2. ADC timing                                                       | 144 |

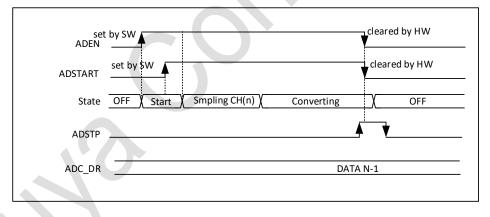

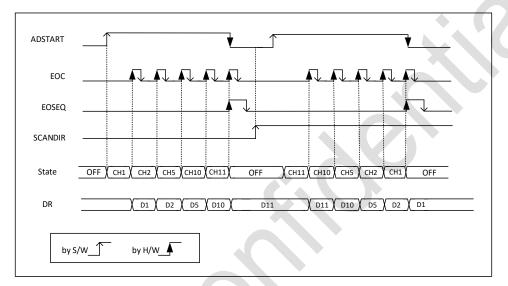

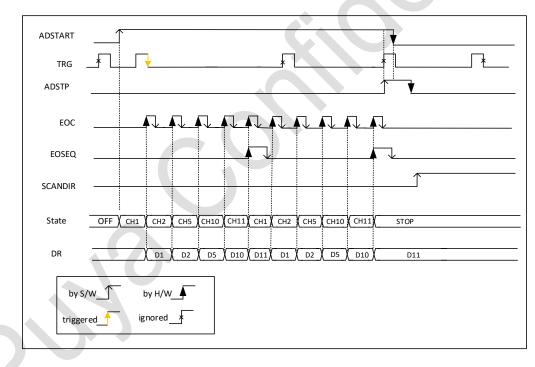

|     | 14.3.13             | 3. Stopping an ongoing conversion (ADSTP)                           | 145 |

| 1   | 4.4.                | Conversion on external trigger and trigger polarity (EXTSEL, EXTEN) | 145 |

|     | 14.4.1.             | Quick transition mode                                               | 146 |

|     | 14.4.2.             | End of conversion / end of sampling phase                           | 146 |

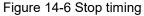

|     | 14.4.3.             | End of conversion sequence (EOSEQ flag)                             | 147 |

|     | 14.4.4.             | Sampling time diagram                                               | 147 |

| 1   | 4.5.                | Data management                                                     | 148 |

|     | 14.5.1.             | Data register and data alignment (ADC_DR, ALIGN)                    | 148 |

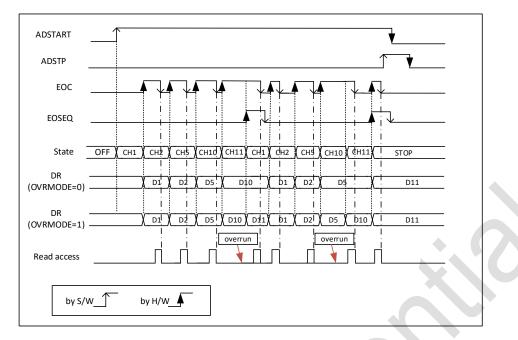

|     | 14.5.2.             | ADC overrun (OVR, OVRMOD)                                           | 149 |

|     | 14.5.3.             | Managing conversion sequences without DMA                           | 150 |

|     | 14.5.4.             | Convert without DMA and overflow detection                          | 150 |

| 1   | 4.6.                | Managing conversion sequences with DMA                              | 150 |

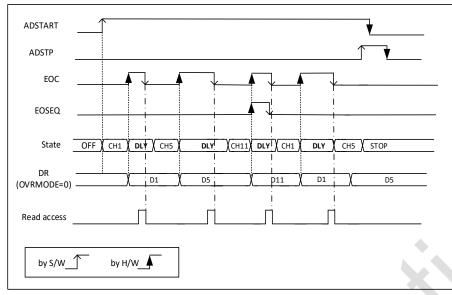

| 14.7. L         | _ow-power features                                              | 151 |

|-----------------|-----------------------------------------------------------------|-----|

| 14.7.1.         | Wait mode conversion                                            | 151 |

| 14.8. <i>A</i>  | Analog watchdog                                                 | 152 |

| 14.8.1.         | ADC_AWD_OUT signal output generation                            | 153 |

| 14.9.           | Temperature sensor and internal reference voltage               | 153 |

| 14.10. <i>A</i> | ADC interrupts                                                  | 155 |

| 14.11. <i>A</i> | ADC registers                                                   | 155 |

| 14.11.1         | ADC interrupt and status register (ADC_ISR)                     | 155 |

| 14.11.2         | ADC interrupt enable register (ADC_IER)                         | 156 |

| 14.11.3         | $\mathbf{U}$                                                    |     |

| 14.11.4         | $\mathbf{c}$                                                    | 158 |

| 14.11.5         | ADC configuration register 2 (ADC_CFGR2)                        |     |

| 14.11.6         | 1 5 ( = )                                                       |     |

| 14.11.7         | i 5 ( _ ,                                                       |     |

| 14.11.8         | ADC watchdog threshold register (ADC_TR)                        | 162 |

| 14.11.9         | <b>o</b> ( <b>i i i i</b>                                       |     |

| 14.11.1         |                                                                 |     |

| 14.11.1         | 1. ADC sequence select register 1 (ADC _ SEQR1)                 | 164 |

| 14.11.1         | 2. ADC data register (ADC_DR)                                   | 165 |

| 14.11.1         | 3. ADC calibration configuration and status register (ADC_CCSR) | 165 |

| 14.11.1         | 4. ADC common configuration register (ADC_CCR)                  | 166 |

|                 | parator (COMP)                                                  |     |

| 15.1. I         | ntroduction                                                     | 168 |

| 15.2. (         | COMP main features                                              | 168 |

| 15.3. (         | COMP functional description                                     | 169 |

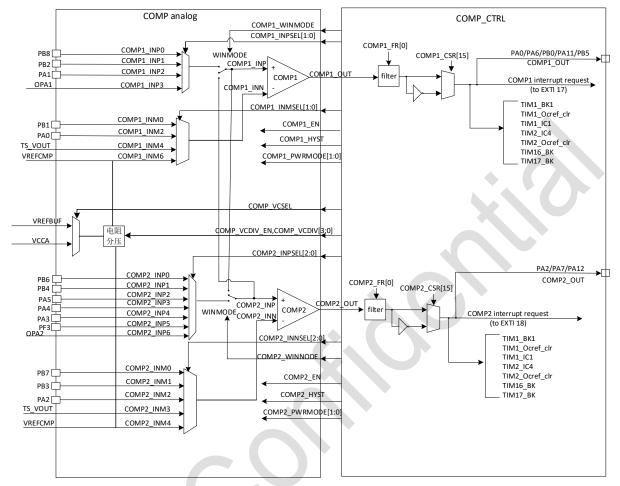

| 15.3.1.         | COMP block diagram                                              | 169 |

| 15.3.2.         | COMP pins and internal signals                                  | 169 |

| 15.3.3.         | COMP reset and clocks                                           | 169 |

| 15.3.4.         | Comparator lock device                                          | 170 |

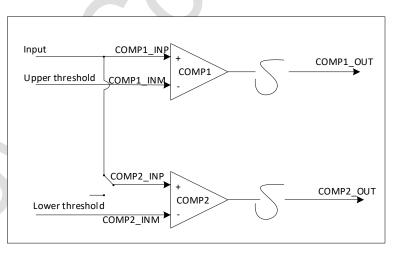

| 15.3.5.         | Window comparator                                               | 170 |

| 15.3.6.         | Hysteresis                                                      | 170 |

| 15.3.7.         | Low-power modes                                                 | 171 |

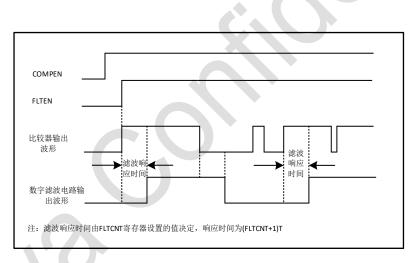

| 15.3.8.         | Comparator filtering                                            | 171 |

| 15.3.9.         | COMP interrupts                                                 | 171 |

| 15.4. (         | COMP registers                                                  | 171 |

| 15.4.1.         | Comparator 1 control and status register (COMP1_CSR)            | 171 |

| 15.4.2.         | Comparator 1 filtering register (COMP1_FR)                      | 173 |

| 15.4.3.         | Comparator 2 control and status register (COMP2_CSR)            | 173 |

| 15.4.4.         | Comparator 2 filtering register (COMP2_FR)                      | 174 |

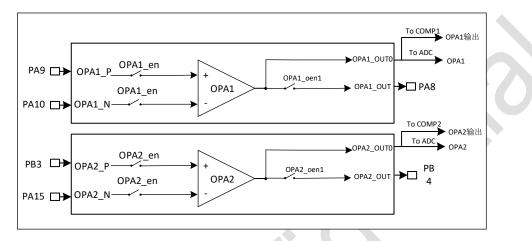

| 16. Oper        | ational amplifier (OPA)                                         |     |

| 16.1.    | Introduction                                     | 175 |

|----------|--------------------------------------------------|-----|

| 16.2.    | OPA main features                                | 175 |

| 16.3.    | OPA functional description                       | 175 |

| 16.4.    | OPA registers                                    | 175 |

| 16.4.1   | . OPA output enable register (OPA _ OENR)        | 175 |

| 16.4.2   | . OPA control register (OPA _ CR)                | 176 |

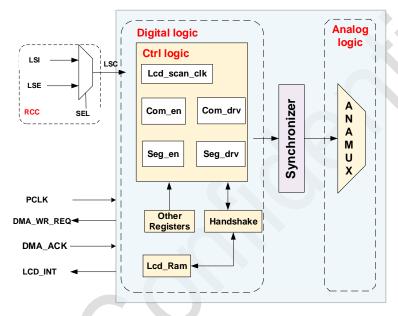

| 17. Liqu | uid crystal display (LCD) controller             | 177 |

| 17.1.    | Introduction                                     |     |

| 17.2.    | LCD main features                                | 177 |

| 17.3.    | LCD function description                         |     |

| 17.3.1   |                                                  |     |

| 17.3.2   | . LCD clock                                      | 178 |

| 17.3.3   | . LCD flushing frequency                         |     |

| 17.3.4   | . LCD display mode                               | 178 |

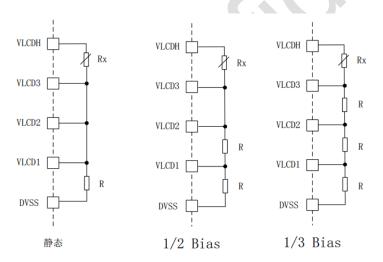

| 17.3.5   | . LCD bias circuit                               | 179 |

| 17.3.6   |                                                  |     |

| 17.3.7   |                                                  |     |

| 17.4.    | LCD register                                     | 181 |

| 17.4.1   | . LCD configuration register 0 (LCD_CR0)         | 181 |

| 17.4.2   | . LCD configuration register 1 (LCD _ CR1)       | 182 |

| 17.4.3   | . Interrupt clear register (LCD _ INTCLR)        | 182 |

| 17.4.4   | . Output configuration register (LCD _ POEN0)    | 183 |

| 17.4.5   | . Output configuration register 1 (LCD _ POEN1)  | 183 |

| 17.4.6   | . LCD_RAM0~3                                     | 183 |

| 17.4.7   | . LCD_RAM4                                       | 184 |

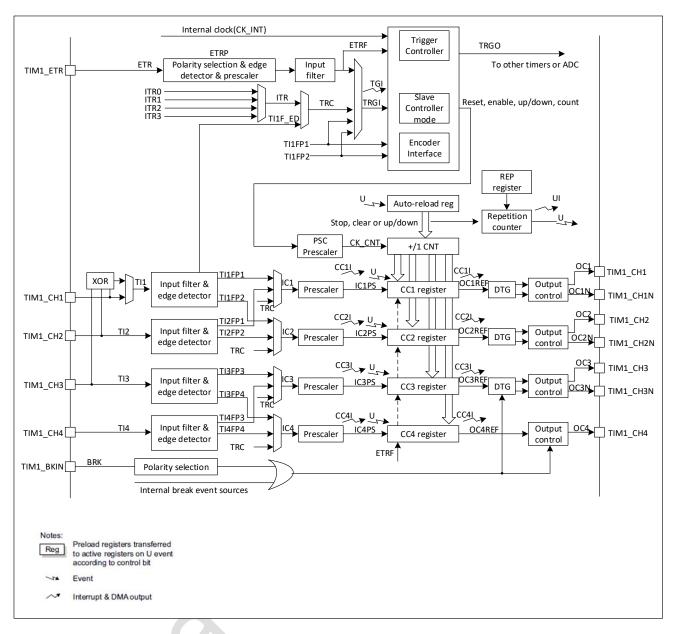

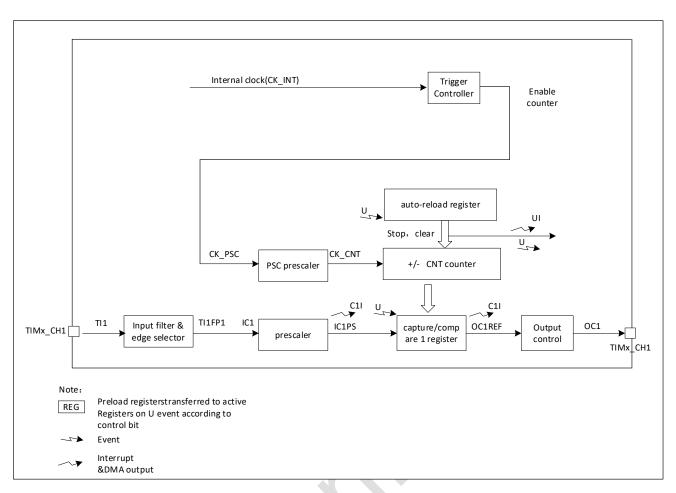

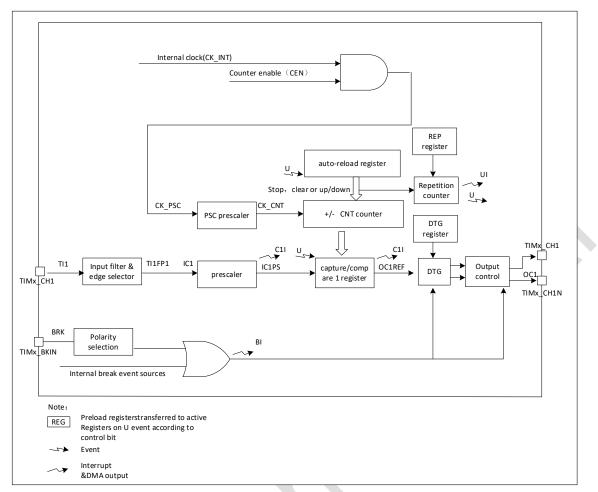

| 18. Adv  | anced-control timers (TIM1)                      | 185 |

| 18.1.    | Introduction                                     | 185 |

| 18.2.    | TIM1 main features                               | 185 |

| 18.3.    | TIM1 functional description                      |     |

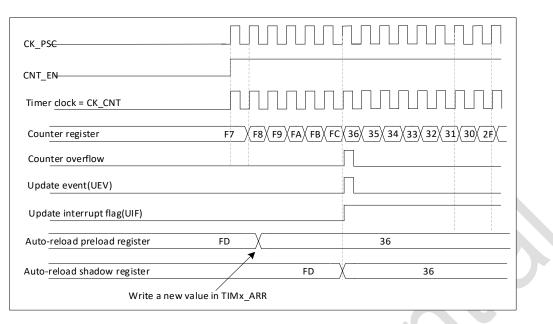

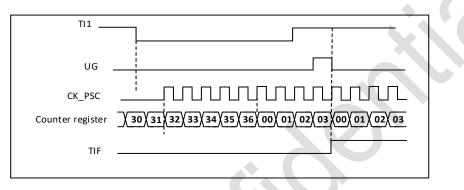

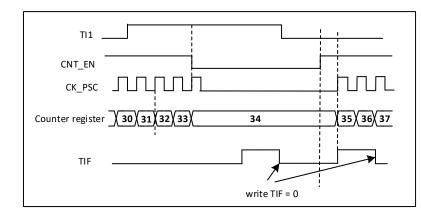

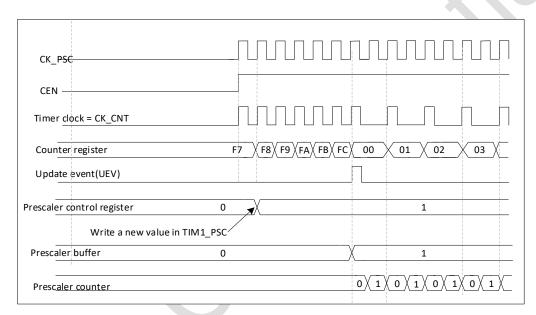

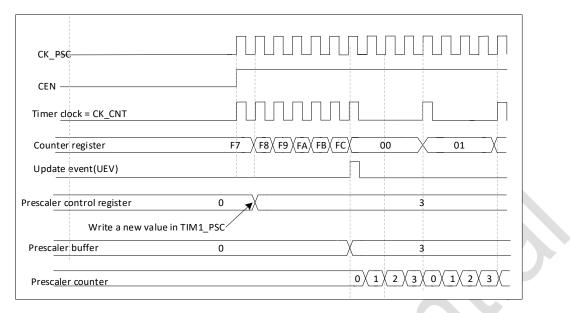

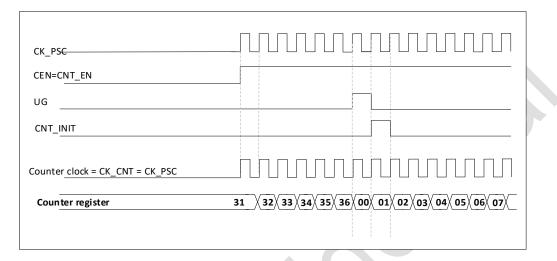

| 18.3.1   | . Time-base unit                                 | 186 |

| 18.3.2   | . Timer enable                                   | 188 |

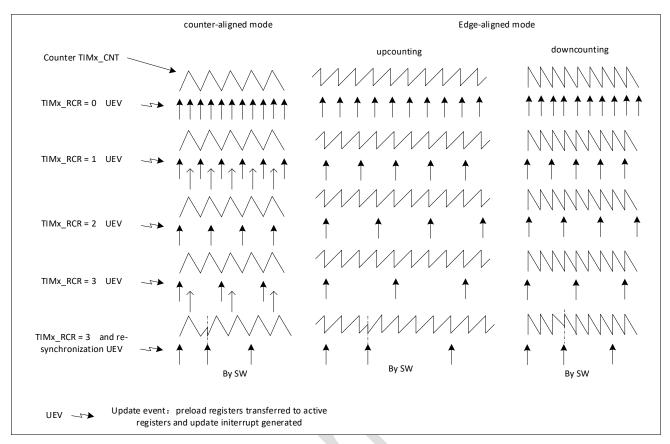

| 18.3.3   | Repetition counter                               | 196 |

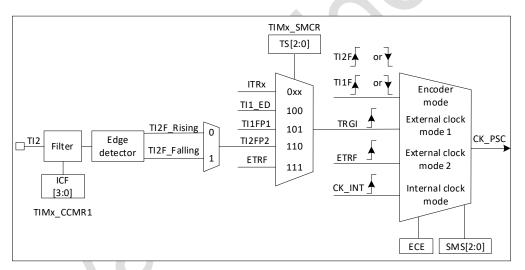

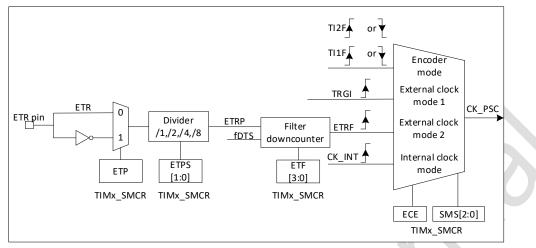

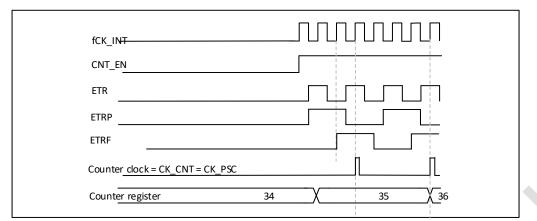

| 18.3.4   | Clock sources                                    | 197 |

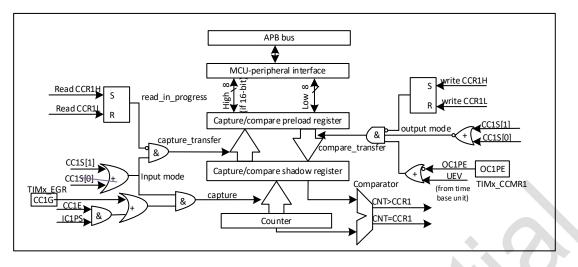

| 18.3.5   | Capture/Compare channels                         | 199 |

| 18.3.6   | . Input capture mode:                            | 201 |

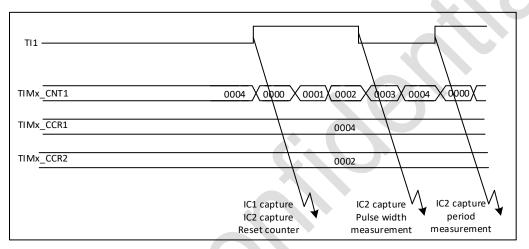

| 18.3.7   | . Input capture mode (PWM input mode)            | 202 |

| 18.3.8   | . Forced output mode                             | 203 |

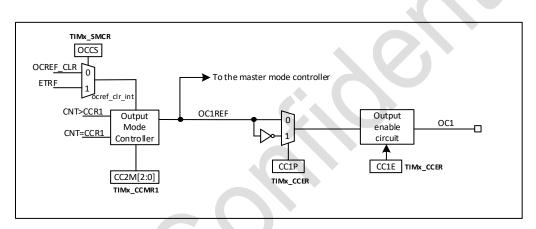

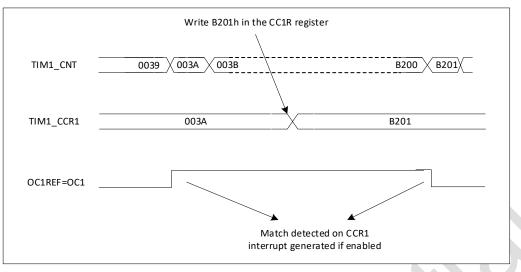

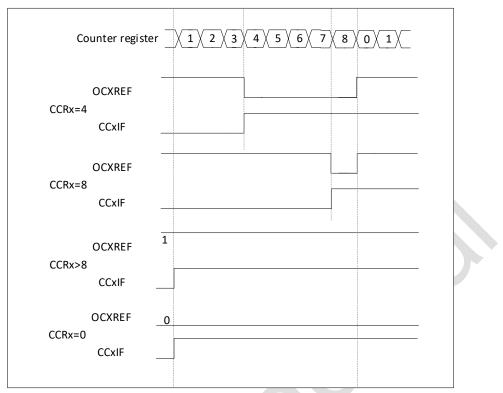

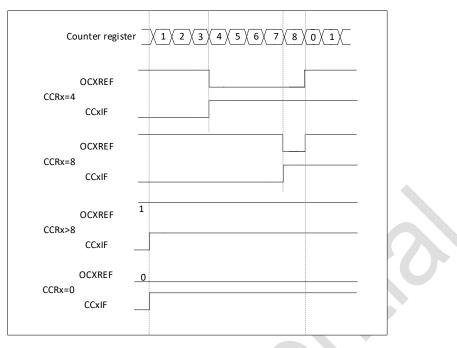

| 18.3.9   | Output compare mode                              | 203 |

| 18.3.1   | 0. PWM mode                                      | 204 |

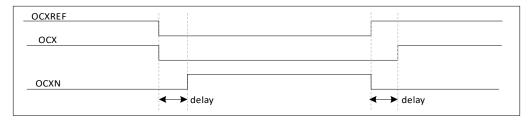

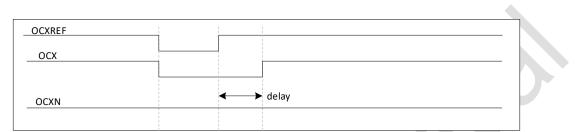

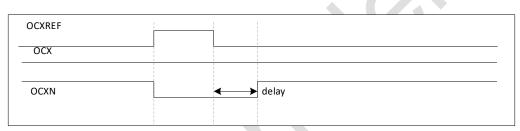

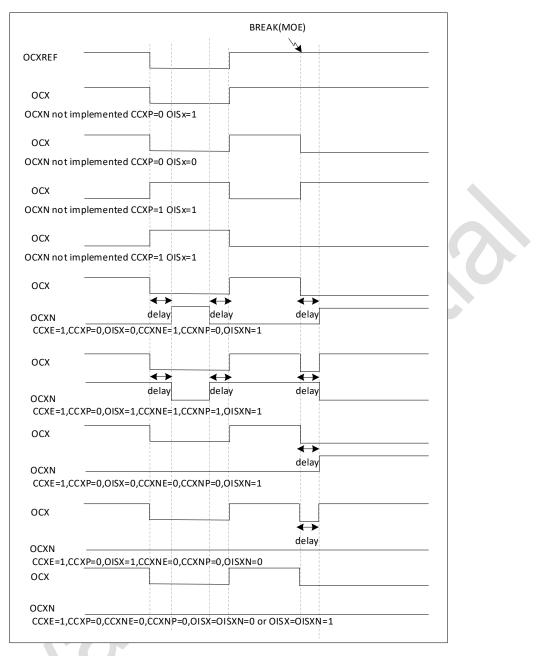

| 18.3.1   | 1. Complementary outputs and dead-time insertion | 207 |

| 18.3.12.  | Using the break function                          | 208 |

|-----------|---------------------------------------------------|-----|

| 18.3.13.  | Clearing the OCxREF signal on an external event   | 210 |

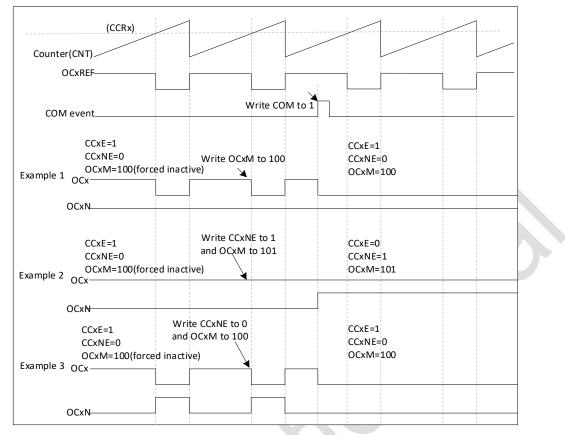

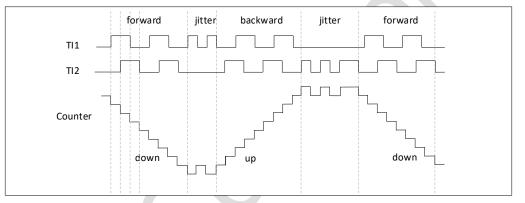

| 18.3.14.  | 6-step PWM generation                             | 211 |

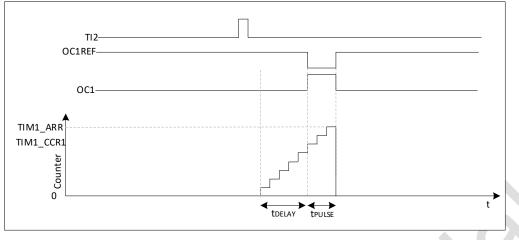

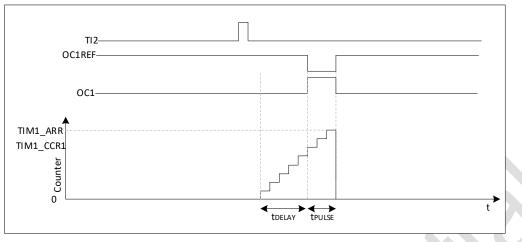

| 18.3.15.  | One-pulse mode                                    | 212 |

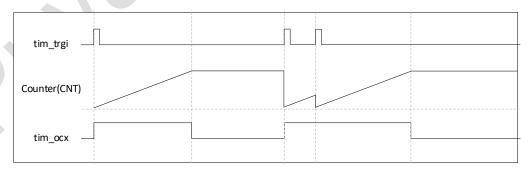

| 18.3.16.  | Retriggerable one pulse mode (OPM)                | 214 |

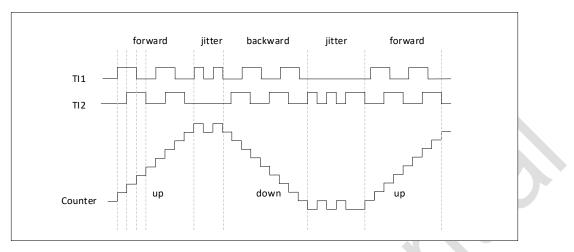

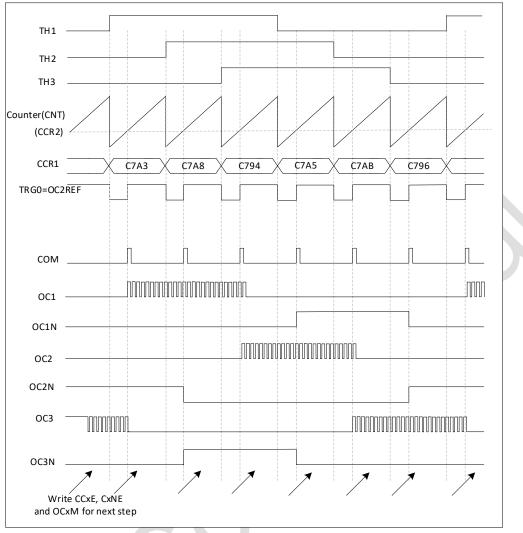

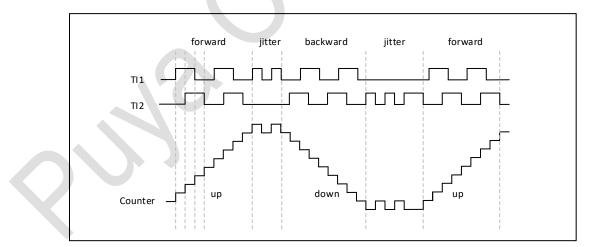

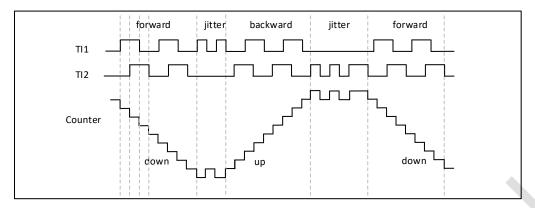

| 18.3.17.  | Encoder interface mode                            | 214 |

| 18.3.18.  | Timer input XOR function                          | 216 |

| 18.3.19.  | Interfacing with Hall sensors                     | 216 |

| 18.3.20.  | TIM and external trigger synchronization          | 218 |

| 18.3.21.  | ,                                                 |     |

| 18.3.22.  | Ŭ                                                 |     |

| 18.4. T   | IM1 registers                                     |     |

| 18.4.1.   | TIM1 control register 1 (TIM1_CR1)                |     |

| 18.4.2.   | TIM1 control register 2 (TIM1_CR2)                |     |

| 18.4.3.   | TIM1 slave mode control register (TIM1_SMCR)      |     |

| 18.4.4.   | TIM1 DMA/interrupt enable register (TIM1 _ DIER)  |     |

| 18.4.5.   | TIM1 status register (TIM1_SR)                    |     |

| 18.4.6.   | TIM1 event generation register (TIM1_EGR)         | 229 |

| 18.4.7.   | TIM1 capture/compare mode register 1 (TIM1_CCMR1) | 230 |

| 18.4.8.   | TIM1 capture/compare mode register 2 (TIM1_CCMR2) | 233 |

| 18.4.9.   | TIM1 capture/compare enable register (TIM1_CCER)  | 234 |

| 18.4.10.  | TIM1 Calculator (TIM1 _ CNT)                      | 236 |

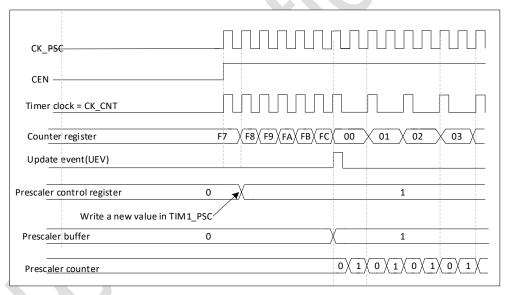

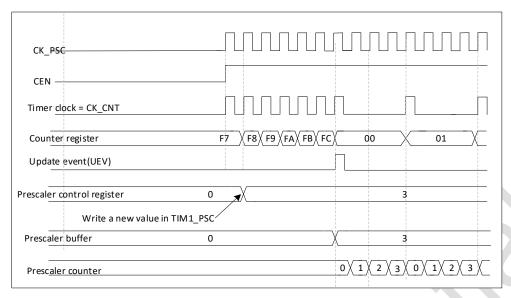

| 18.4.11.  | TIM1 Prescaler (TIM1 _ PSC)                       | 236 |

| 18.4.12.  | TIM1 automatic reload register (TIM1 _ ARR)       | 237 |

| 18.4.13.  | TIM1 Repetition counter register (TIM1_RCR)       | 237 |

| 18.4.14.  | TIM1 capture/compare register 1 (TIM1_CCR1)       | 237 |

| 18.4.15.  | TIM1 capture/compare register 2 (TIM1 _ CCR2)     | 238 |

| 18.4.16.  | TIM1 capture/compare register 3 (TIM1_CCR3)       | 238 |

| 18.4.17.  | TIM1 capture/compare register 4 (TIM1 _ CCR4)     | 239 |

| 18.4.18.  | TIM1 break and dead-time register (TIM1_BDTR)     | 239 |

| 18.4.19.  | TIM1 DMA control register (TIM1_DCR)              | 241 |

| 18.4.20.  | DMA address of TIM1 continuous mode (TIM1 _ DMAR) | 241 |

| 19. Gener | ral-purpose timers (TIM2)                         | 243 |

| 19.1. Ir  | ntroduction to TIM2                               | 243 |

| 19.2. T   | IM2 Main Features                                 | 243 |

| 19.3. T   | IM2 functional description                        | 244 |

| 19.3.1.   | Time-base unit                                    |     |

| 19.3.2.   | Timer enable                                      |     |

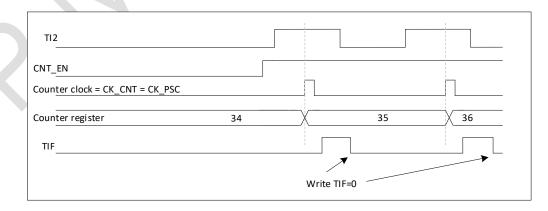

| 19.3.3.   | Clock sources                                     |     |

| 19.3.4.   | Capture/Compare channels                          | 256 |

| 19.3.5.   | Input capture mode:                                 | 257 |

|-----------|-----------------------------------------------------|-----|

| 19.3.6.   | PWM input mode                                      | 258 |

| 19.3.7.   | Forced output mode                                  | 259 |

| 19.3.8.   | Output compare mode                                 | 259 |

| 19.3.9.   | Pulse width modulation (PWM) mode                   | 261 |

| 19.3.10.  | One-pulse mode                                      | 263 |

| 19.3.11.  | Encoder interface mode                              | 265 |

| 19.3.12.  | Timer input XOR function                            | 267 |

| 19.3.13.  | Synchronization of timer and externally triggered   | 267 |

| 19.3.14.  | Timer synchronization                               | 270 |

| 19.3.15.  | 5                                                   |     |

| 19.4. R   | Register Description                                | 275 |

| 19.4.1.   | TIM2 control register 1 (TIM2 _ CR1)                |     |

| 19.4.2.   | TIM2 control register 2 (TIM2_CR2)                  |     |

| 19.4.3.   | TIM2 slave mode control register (TIM2_SMCR)        | 277 |

| 19.4.4.   | TIM2DMA/interrupt enable register (TIM2 _ DIER)     |     |

| 19.4.5.   | TIM2 status register (TIM2_SR)                      |     |

| 19.4.6.   | TIM2 event generation register (TIM2_EGR)           | 281 |

| 19.4.7.   | TIM2 capture/compare mode register 1 (TIM2 _ CCMR1) | 282 |

| 19.4.8.   | TIM2 capture/compare mode register 2 (TIM2 _ CCMR2) | 285 |

| 19.4.9.   | TIM2 capture/compare enable register (TIM2 _ CCER)  | 287 |

| 19.4.10.  | TIM2 Counter (TIM2 _ CNT)                           | 288 |

| 19.4.11.  | TIM2 Prescaler (TIM2 _ PSC)                         | 288 |

| 19.4.12.  | TIM2 auto-reload register (TIM2_ARR)                | 288 |

| 19.4.13.  | TIM2 capture/compare register 1 (TIM2_CCR1)         | 289 |

| 19.4.14.  | TIM2 capture/compare register 2 (TIM2_CCR2)         | 289 |

| 19.4.15.  | TIM2 capture/compare register 3 (TIM2_CCR3)         | 289 |

| 19.4.16.  | TIM2 capture/compare register 4 (TIM2_CCR4)         | 290 |

| 19.4.17.  | TIM2 DMA control register (TIM2 _ DCR)              | 290 |

| 19.4.18.  | DMA address of TIM2 continuous mode (TIM2 _ DMAR)   | 291 |

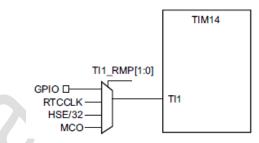

| 20. Gener | ral-purpose timer (TIM14)                           | 292 |

| 20.1. T   | IM14 introduction                                   | 292 |

| 20.2. T   | IM14 main features                                  | 292 |

| 20.3. T   | IM14 functional description                         | 293 |

| 20.3.1.   | Time-base unit                                      | 293 |

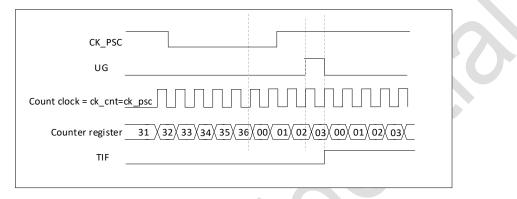

| 20.3.2.   | Counting pattern                                    | 295 |

| 20.3.3.   | Clock sources                                       | 298 |

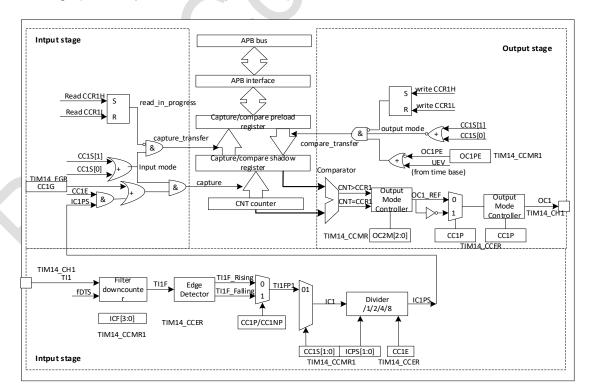

| 20.3.4.   | Capture/Compare channels                            | 298 |

| 20.3.5.   | Input capture mode:                                 | 299 |

| 20.3.6.   | Forced output mode                                  | 300 |

| 20.3.7.  | Output compare mode                                         |  |

|----------|-------------------------------------------------------------|--|

| 20.3.8.  | Pulse width adjustment (PWM) mode                           |  |

| 20.3.9.  | Debug mode                                                  |  |

| 20.4. T  | IM14 registers                                              |  |

| 20.4.1.  | TIM14 control register 1 (TIM14_CR1)                        |  |

| 20.4.2.  | TIM14 DMA/interrupt enable register (TIM14 _ DIER)          |  |

| 20.4.3.  | TIM14 status register (TIM14_SR)                            |  |

| 20.4.4.  | TIM14 event generation register (TIM14_EGR)                 |  |

| 20.4.5.  | TIM14 capture/compare mode register 1 (TIM14_CCMR1)         |  |

| 20.4.6.  | TIM14 capture/compare enable register (TIM14_CCER)          |  |

| 20.4.7.  | TIM14 Counter (TIM14 _ CNT)                                 |  |

| 20.4.8.  | TIM14 Prescaler (TIM14 _ PSC)                               |  |

| 20.4.9.  | TIM14 auto-reload register (TIM14_ARR)                      |  |

| 20.4.10. | 1 1 5 ( = )                                                 |  |

| 20.4.11. | 1 5 ( = /                                                   |  |

|          | ral purpose timer (TIM16/17)                                |  |

|          | lain features                                               |  |

| 21.2. F  | unctional Description                                       |  |

| 21.2.1.  | Time-base unit                                              |  |

| 21.2.2.  | Timer enable                                                |  |

| 21.2.3.  | Repetition counter                                          |  |

| 21.2.4.  | Clock sources                                               |  |

| 21.2.5.  | Capture/Compare channels                                    |  |

| 21.2.6.  | Input capture mode:                                         |  |

| 21.2.7.  | Forced output mode                                          |  |

| 21.2.8.  | Output compare mode                                         |  |

| 21.2.9.  | PWM mode                                                    |  |

| 21.2.10. |                                                             |  |

| 21.2.11. | 5                                                           |  |

| 21.2.12. |                                                             |  |

| 21.3. Т  | IM16/TIM17 register                                         |  |

| 21.3.1.  | TIM16/17 control register 1 (TIMx _ CR1)                    |  |

| 21.3.2.  | TIM16/17 control register 2 (TIMx _ CR2)                    |  |

| 21.3.3.  | TIM16/17 DMA/interrupt enable register (TIM16/17 _ DIER)    |  |

| 21.3.4.  | TIM16/17 status register (TIM16/17 _ SR)                    |  |

| 21.3.5.  | TIM16/17 event generation register (TIM16/17 _ EGR)         |  |

| 21.3.6.  | TIM16/17 capture/compare mode register 1 (TIM16/17 _ CCMR1) |  |

| 21.3.7.  | TIM16/17 Capture/Compare enable register (TIM16/17 _ CCER)  |  |

| 21.3.8.  | TIM16/17 Calculator (TIM16/17 _ CNT)                        |  |

| 21.3.9.  | TIM16/17 Prescaler (TIM16/17 _ PSC)                         |  |

| 21.3.1    | 0. TIM16/17 automatic reload register (TIM16/17 _ ARR)        |     |

|-----------|---------------------------------------------------------------|-----|

| 21.3.1    | 1. TIM16/17 repetition counter register (TIM16/17 _ RCR)      |     |

| 21.3.1    | 2. TIM16/17 capture/compare register 1 (TIM16/17 _ CCR1)      |     |

| 21.3.1    | 3. TIM16/17 brake and dead time register (TIM16/17 _ BDTR)    |     |

| 21.3.1    | 4. TIM16/17 DMA control register (TIM16/17 _ DCR)             |     |

| 21.3.1    | 5. DMA address for TIM16/17 continuous mode (TIM16/17 _ DMAR) |     |

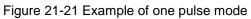

| 22. Infra | ared interface (IRTIM)                                        |     |

| 23. Low   | /-power timer (LPTIM)                                         |     |

| 23.1.     | Introduction                                                  | 341 |

| 23.2.     | Main features                                                 |     |

| 23.3.     | Functional Description                                        |     |

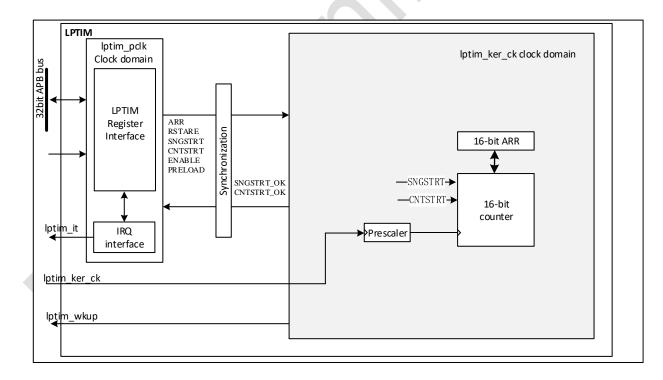

| 23.3.1    | . LPTIM block diagram                                         |     |

| 23.3.2    |                                                               |     |

| 23.3.3    |                                                               |     |

| 23.3.4    |                                                               |     |

| 23.3.5    | 5                                                             |     |

| 23.3.6    | 5 1                                                           |     |

| 23.3.7    | Enable timer                                                  |     |

| 23.3.8    | . Timer counter reset                                         |     |

| 23.3.9    | 5                                                             |     |

| 23.4.     | LPTIM Description                                             |     |

| 23.5.     | LPTIM interrupts                                              |     |

| 23.6.     | Register Description                                          |     |

| 23.6.1    | . LPTIM interrupt and status register (LPTIM_ISR)             |     |

| 23.6.2    | . LPTIM interrupt clear register (LPTIM _ ICR)                |     |

| 23.6.3    | . LPTIM interrupt enable register (LPTIM_IER)                 |     |

| 23.6.4    | . LPTIM configuration register (LPTIM_CFGR)                   |     |

| 23.6.5    | . LPTIM control register (LPTIM_CR)                           |     |

| 23.6.6    | . LPTIM autoreload register (LPTIM_ARR)                       |     |

| 23.6.7    | . LPTIM counter register (LPTIM_CNT)                          |     |

| 24. Inde  | ependent watchdog (IWDG)                                      |     |

| 24.1.     | Introduction                                                  |     |

| 24.2.     | IWDG main features                                            |     |

| 24.3.     | IWDG functional description                                   |     |

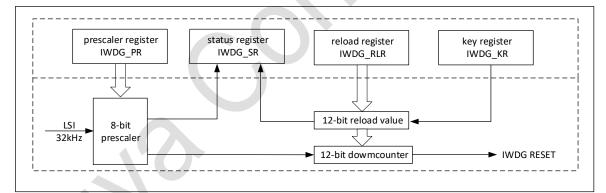

| 24.3.1    | IWDG block diagram                                            |     |

| 24.3.2    | Hardware watchdog                                             |     |

| 24.3.3    | Register access protection                                    | 350 |

| 24.3.4    | Debug mode                                                    | 350 |

| 24.3.5    | Stop mode                                                     | 350 |

| 24.4.     | IWDG registers                                                | 350 |

|     | 24.4.1 | . IWDG key register (IWDG_KR)                     | 350 |

|-----|--------|---------------------------------------------------|-----|

|     | 24.4.2 | . IWDG prescaler register (IWDG_PR)               | 350 |

|     | 24.4.3 | . IWDG reload register (IWDG_RLR)                 | 351 |

|     | 24.4.4 | . Status register (WWDG_SR)                       | 351 |

| 25. | Win    | dow watchdog (WWDG)                               | 352 |

| 2   | 25.1.  | Introduction                                      | 352 |

| 2   | 25.2.  | WWDG main features                                | 352 |

| 2   | 25.3.  | WWDG functional description                       |     |

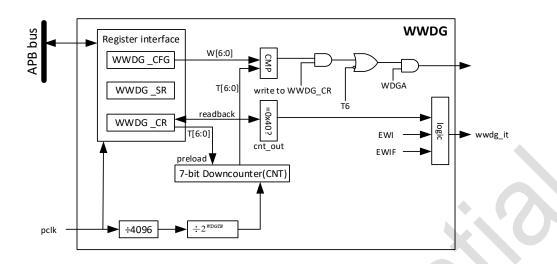

|     | 25.3.1 | . WWDG architecture block diagram                 |     |

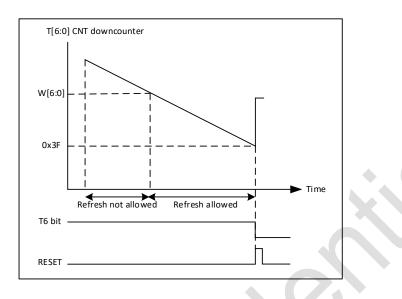

|     | 25.3.2 | 5                                                 |     |

|     | 25.3.3 |                                                   |     |

|     | 25.3.4 | Advanced watchdog interrupt function              |     |

|     | 25.3.5 | 5 1 5                                             |     |

| 2   | 25.4.  | WWDG registers                                    |     |

|     | 25.4.1 | 5 ( _ /                                           |     |

|     | 25.4.2 | 5 5 ( = /                                         |     |

|     | 25.4.3 | 5 ( _ /                                           |     |

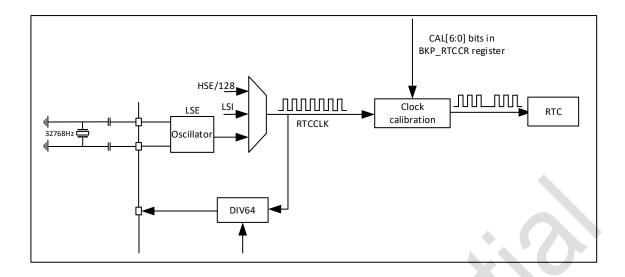

| 26. | Rea    | I-time clock (RTC)                                |     |

| 2   | 26.1.  | Introduction                                      |     |

| 2   | 26.2.  | Main features                                     |     |

| 2   | 26.3.  | RTC functional description                        |     |

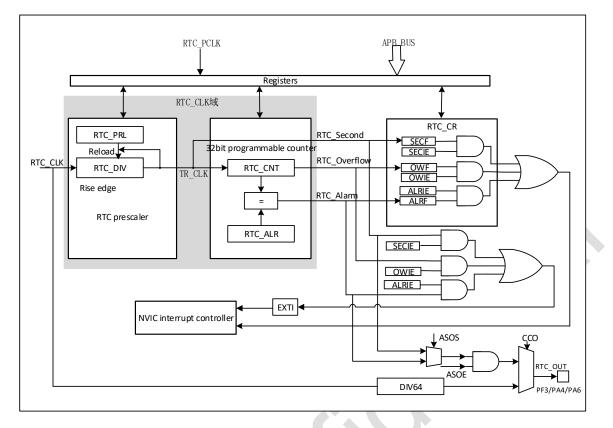

|     | 26.3.1 |                                                   |     |

|     | 26.3.2 |                                                   |     |

|     | 26.3.3 | 5                                                 |     |

|     | 26.3.4 | Configure the RTC register                        | 358 |

|     | 26.3.5 |                                                   |     |

|     | 26.3.6 |                                                   |     |

| 2   | 26.4.  | RTC registers                                     |     |

|     | 26.4.1 | <b>5</b> ( <b>– )</b>                             |     |

|     | 26.4.2 | <b>S</b> ( <b>- )</b>                             |     |

|     | 26.4.3 |                                                   |     |

|     | 26.4.4 |                                                   |     |

|     | 26.4.5 |                                                   |     |

|     | 26.4.6 |                                                   |     |

|     | 26.4.7 |                                                   |     |

|     | 26.4.8 |                                                   |     |

|     | 26.4.9 |                                                   |     |

|     | 26.4.1 |                                                   |     |

| _   | 26.4.1 |                                                   |     |

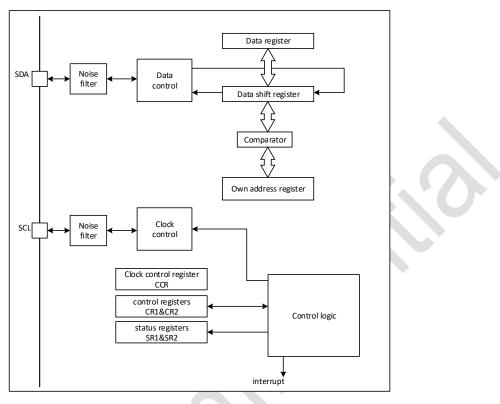

| 27. | Inte   | r-integrated circuit (I <sup>2</sup> C) interface | 366 |

| 27.1.    | Introduction                                                 |     |

|----------|--------------------------------------------------------------|-----|

| 27.2.    | Main features                                                |     |

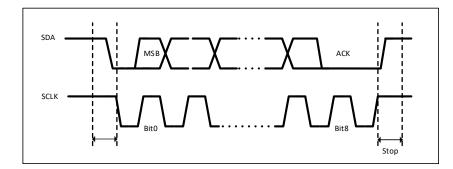

| 27.3.    | I <sup>2</sup> C functional description                      |     |

| 27.3.1   | . I <sup>2</sup> C block diagram                             |     |

| 27.3.2   | . Mode selection                                             |     |

| 27.3.3   | . I <sup>2</sup> C initialization                            |     |

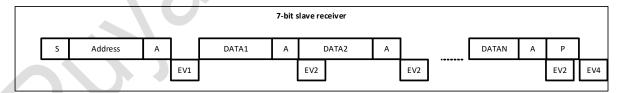

| 27.3.4   | . I <sup>2</sup> C slave mode                                |     |

| 27.3.5   | . I <sup>2</sup> C master mode                               |     |

| 27.3.6   | . Error conditions                                           |     |

| 27.3.7   |                                                              |     |

| 27.3.8   | -                                                            |     |

| 27.3.9   | . Packet error check                                         |     |

| 27.4.    | I <sup>2</sup> C interrupts                                  |     |

| 27.5.    | I2C registers                                                |     |

| 27.5.1   | 5 ( _ /                                                      |     |

| 27.5.2   | 5 ( = /                                                      |     |

| 27.5.3   | 5 ( = /                                                      |     |

| 27.5.4   | 5 ( = )                                                      |     |

| 27.5.5   | 5 ( _ /                                                      |     |

| 27.5.6   | 5 ( = /                                                      |     |

| 27.5.7   | . I <sup>2</sup> C status register 2 (I2C_SR2)               |     |

| 27.5.8   | . I2C Clock control register (I2C_CCR)                       |     |

| 27.5.9   | . I <sup>2</sup> C TRISE register (I2C_TRISE)                |     |

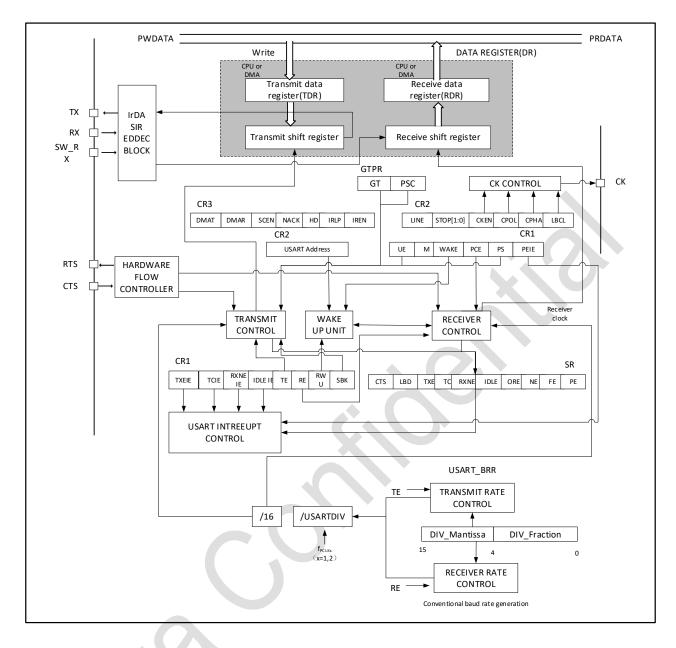

| 28. Univ | versal synchronous asynchronous receiver transmitter (USART) |     |

| 28.1.    | Introduction                                                 |     |

| 28.2.    | USART main features                                          |     |

| 28.3.    | USART functional description                                 |     |

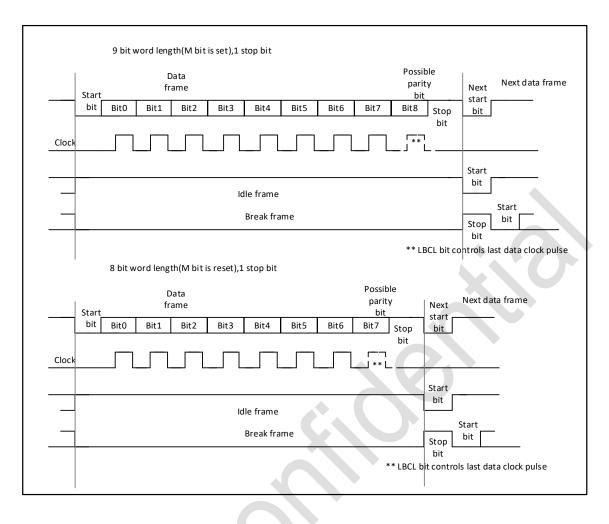

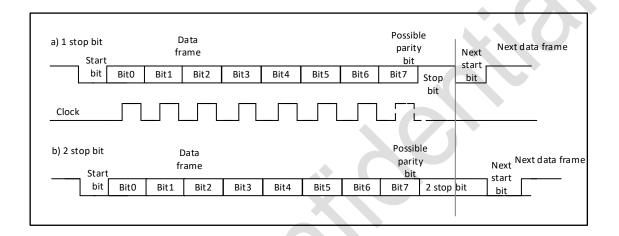

| 28.3.1   | . USART character description                                | 391 |

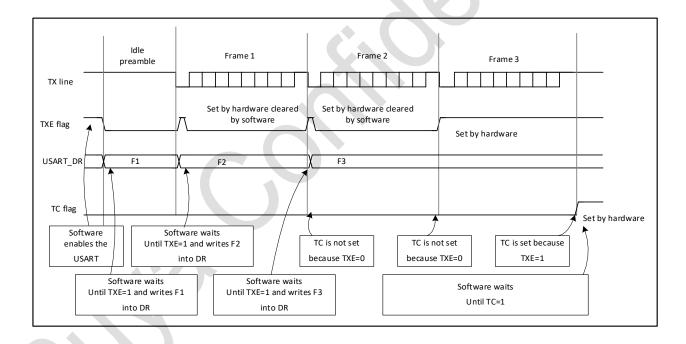

| 28.3.2   | . Transmitter                                                |     |

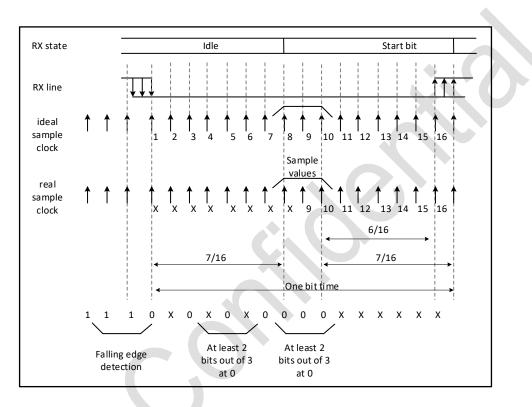

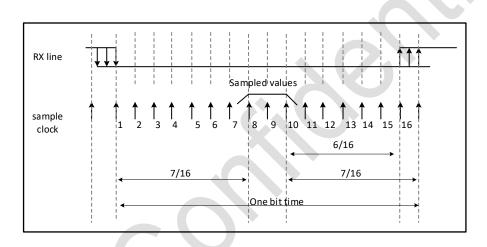

| 28.3.3   | . Receiver                                                   |     |

| 28.3.4   | USART baud rate generation                                   |     |

| 28.3.5   | . Tolerance of the USART receiver to clock deviation         |     |

| 28.3.6   | USART Auto baud rate detection                               |     |

| 28.3.7   | . Multiprocessor communication                               | 401 |

| 28.3.8   | . USART synchronous mode                                     |     |

| 28.3.9   | . Single-wire Half-duplex communications                     |     |

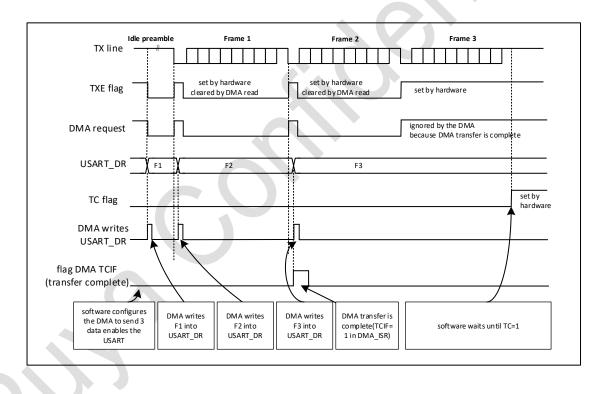

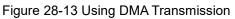

| 28.3.1   | 0. Continuous Communication Using DMA                        |     |

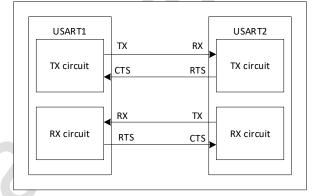

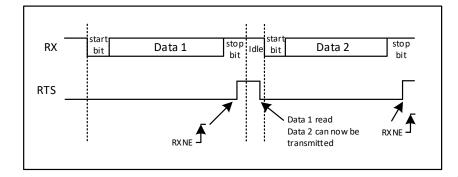

| 28.3.1   | 1. Hardware flow control                                     |     |

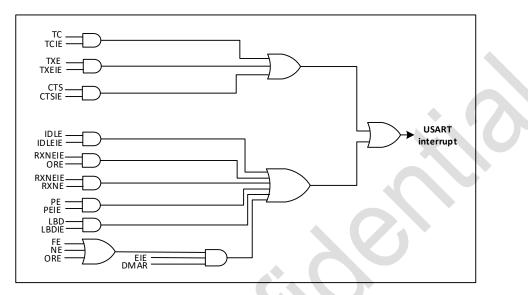

| 28.4.    | USART interrupts                                             |     |

| 28.5.    | USART register                                               |     |

|     | 28.5.1.  | USART status register (USART_SR)                | 409 |

|-----|----------|-------------------------------------------------|-----|

|     | 28.5.2.  | USART data register (USART_DR)                  | 411 |

|     | 28.5.3.  | Baud rate register (USART_BRR)                  | 412 |

|     | 28.5.4.  | USART control register 1 (USART_CR1)            | 412 |

|     | 28.5.5.  | USART control register 2 (USART_CR2)            | 413 |

|     | 28.5.6.  | USART control register 3 (USART_CR3)            | 414 |

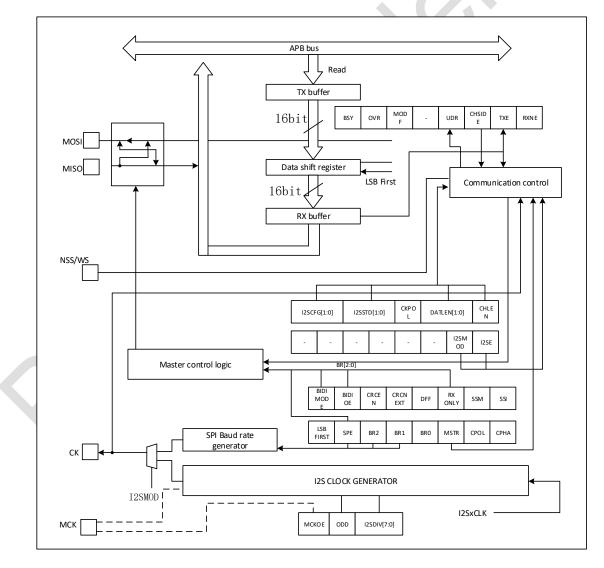

| 29. | Serial   | peripheral interface/I2S (SPI/I2S)              | 416 |

| 2   | .9.1. Ir | ntroduction                                     | 416 |

| 2   | 29.2. N  | 1ain features                                   | 416 |

|     | 29.2.1.  |                                                 |     |

|     |          | I2S main features                               |     |

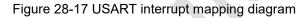

| 2   | .9.3. S  | PI functional description                       | 418 |

|     | 29.3.1.  | Overview                                        |     |

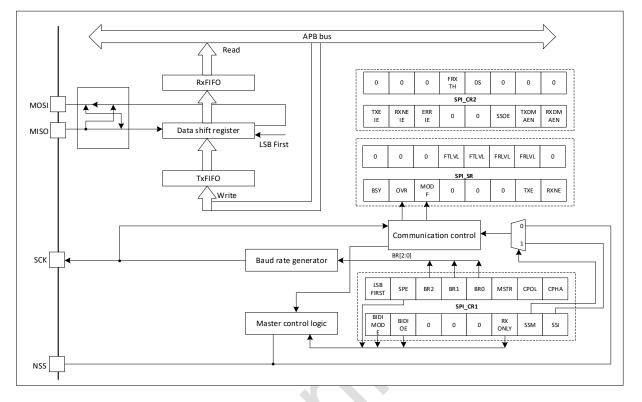

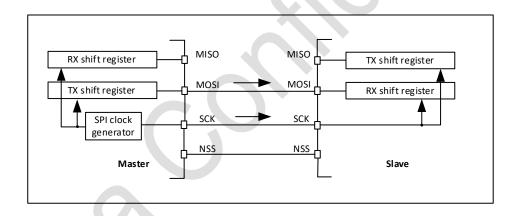

|     | 29.3.2.  | Communications between one master and one slave |     |

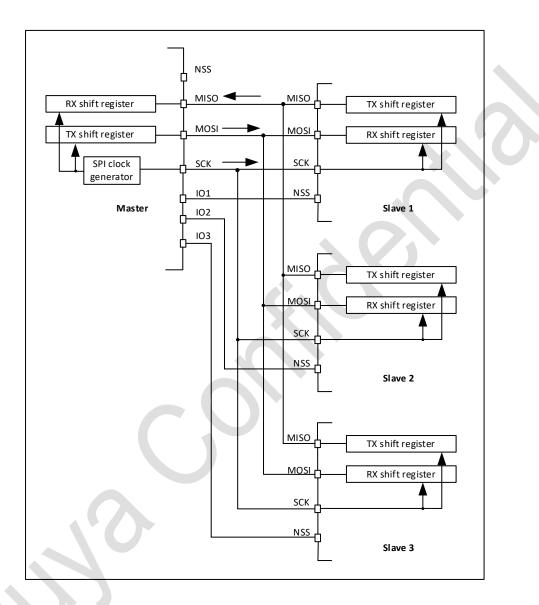

|     | 29.3.3.  | Multi-slave communication                       | 421 |

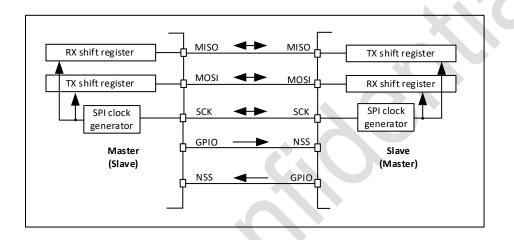

|     | 29.3.4.  | Multi-master communication                      |     |

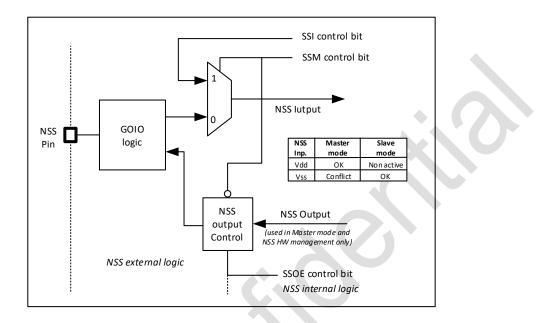

|     | 29.3.5.  | Slave Select (NSS) pin management               |     |

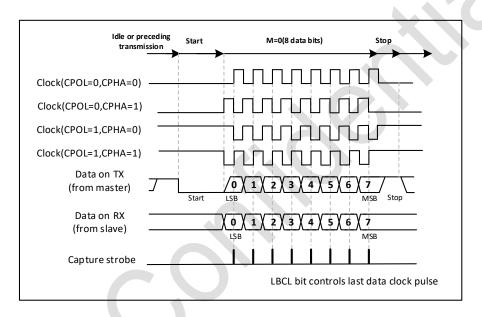

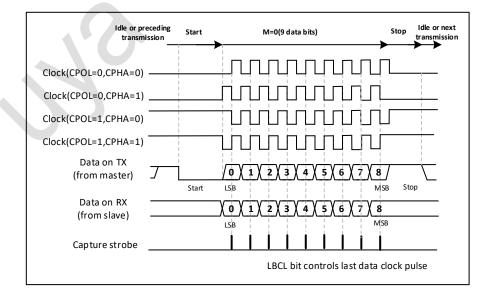

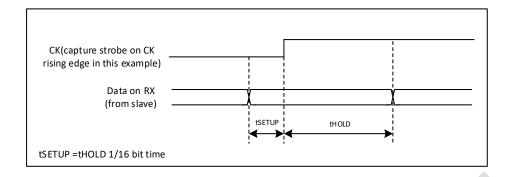

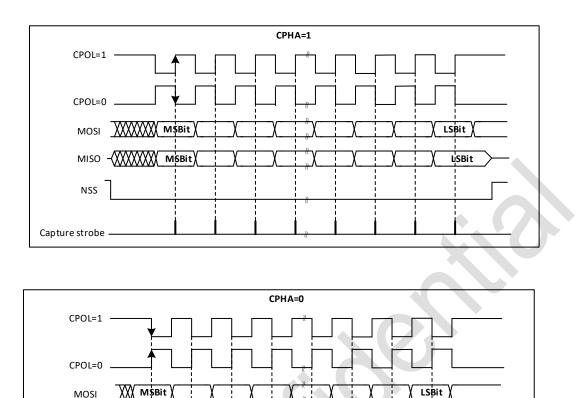

|     | 29.3.6.  | Communication formats                           |     |

|     | 29.3.7.  | Configuration of SPI                            |     |

|     | 29.3.8.  | Procedure for enabling SPI                      | 425 |

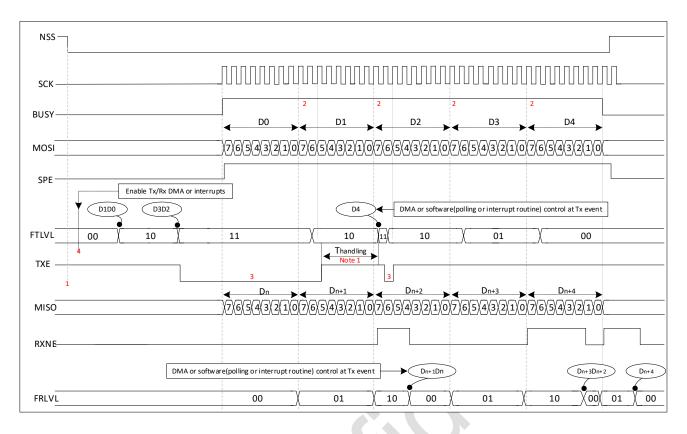

|     | 29.3.9.  | Data transmission and reception procedures      | 425 |

|     | 29.3.10. | Status flags                                    | 429 |

|     | 29.3.11. | Error flags                                     | 430 |

|     | 29.3.12. | SPI interrupts                                  | 431 |

|     | 29.3.13. | SPI CRC                                         | 431 |

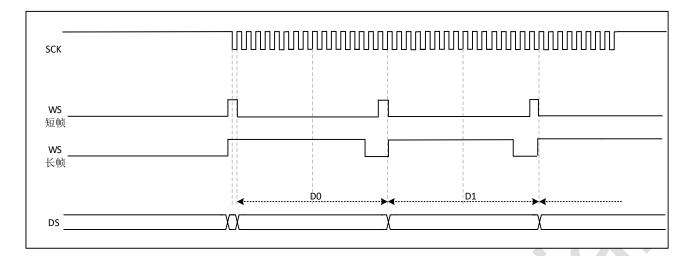

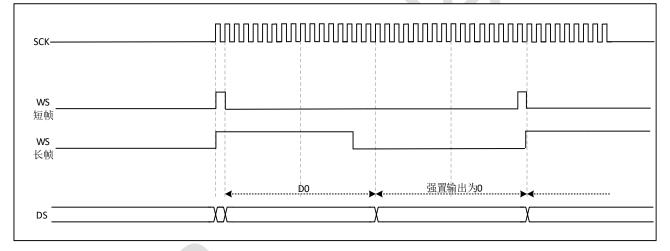

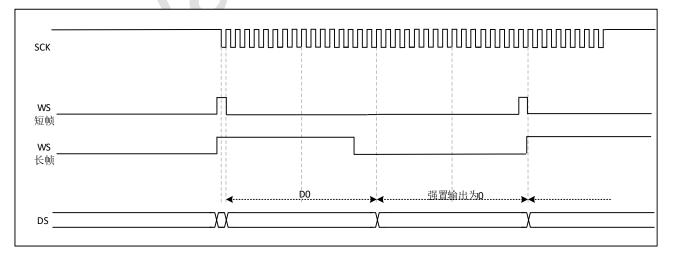

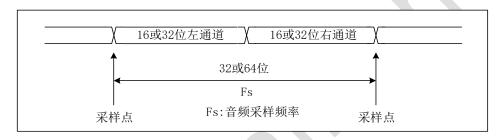

| 2   | 29.4. I2 | 2S functional description                       | 432 |

|     | 29.4.1.  | General Description                             | 432 |

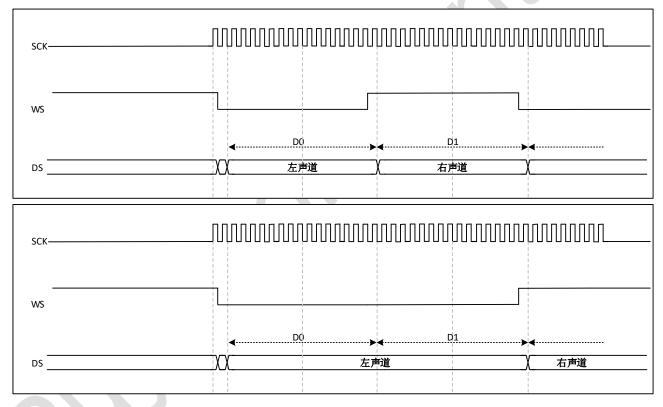

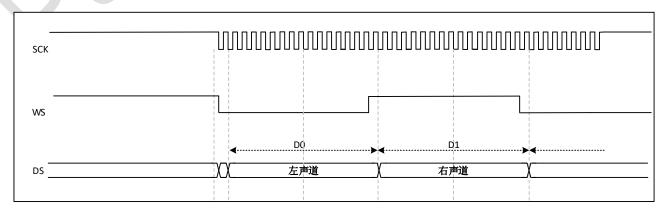

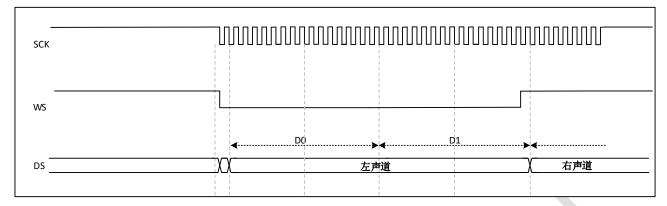

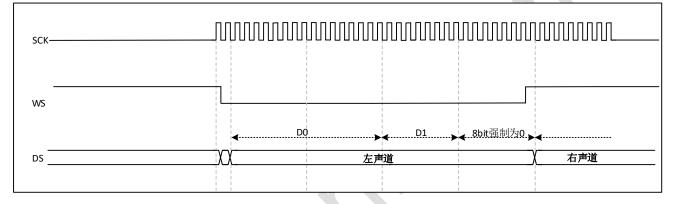

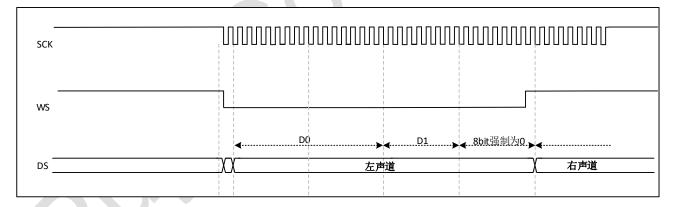

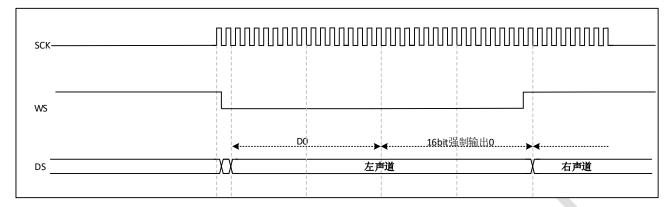

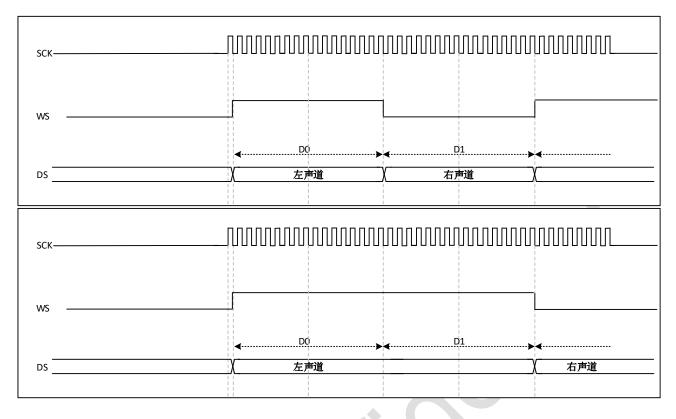

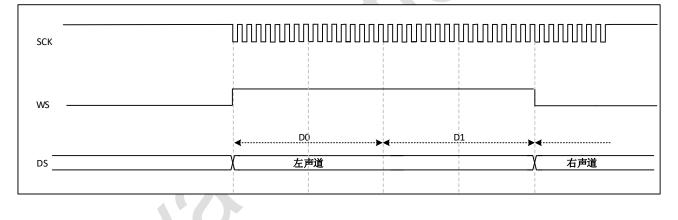

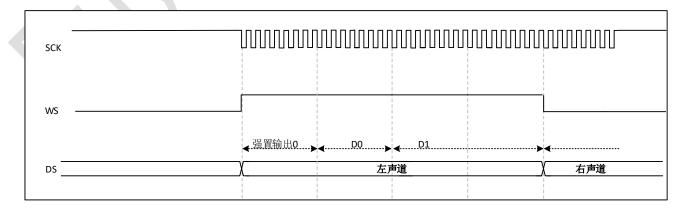

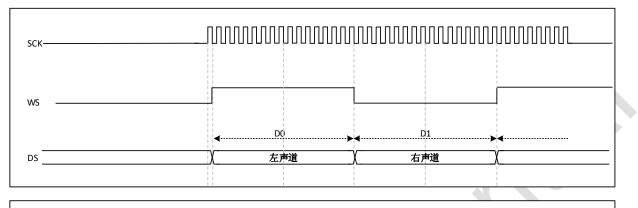

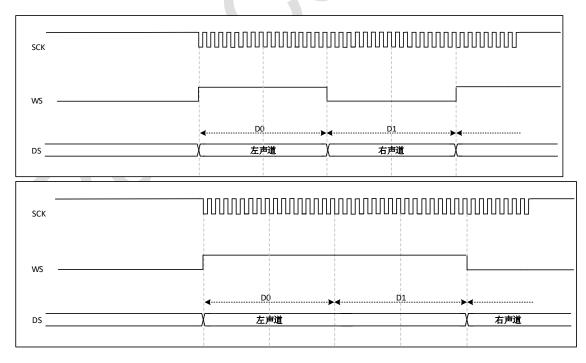

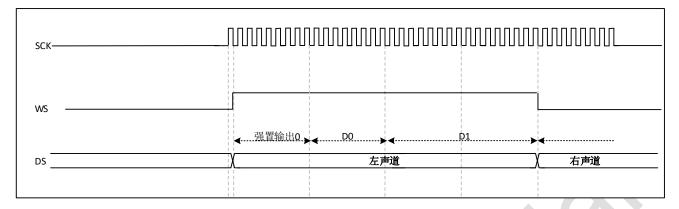

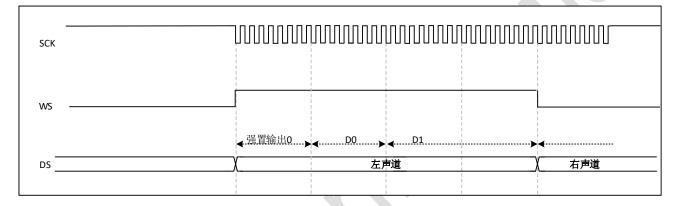

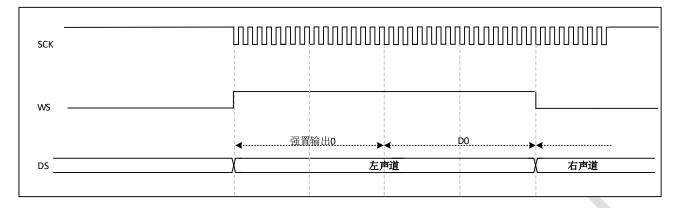

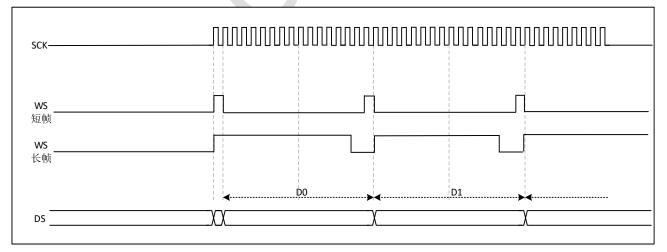

|     | 29.4.2.  | Supports audio protocols                        | 433 |

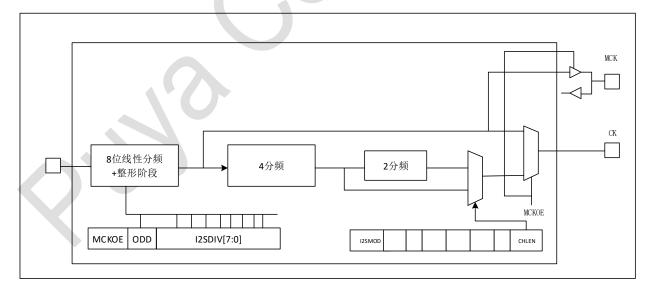

|     | 29.4.3.  | Clock generator                                 | 443 |

|     | 29.4.4.  | Transmission                                    | 444 |

|     | 29.4.5.  | I2S flag bit                                    | 447 |

|     | 29.4.6.  | I2S DMA                                         | 448 |

|     | 29.4.7.  | I2S Interrupt                                   | 449 |

| 2   | 9.5. S   | PI/I2S register                                 | 449 |

|     | 29.5.1.  | SPI control register 1 (SPI_CR1)                | 449 |

|     | 29.5.2.  | SPI control register 2 (SPI_CR2)                | 451 |

|     | 29.5.3.  | SPI status register (SPI_SR)                    | 451 |

|     | 29.5.4.  | SPI data register (SPI_DR)                      | 453 |

|     | 29.5.5.  | SPI CRC polynomial register (SPI _ CRCPR)       | 453 |

|     | 29.5.6.  | SPI Tx CRC register (SPI _ TXCRC)               | 453 |

|     | 29.5.7 | . SPI Tx CRC register (SPI _ TXCRC)                   | 454 |

|-----|--------|-------------------------------------------------------|-----|

|     | 29.5.8 | . SPI _ I2S configuration register (SPI _ I2S _ CFGR) | 454 |

|     | 29.5.9 | . SPI _ I2S prescaler register (SPI _ I2SPR)          | 456 |

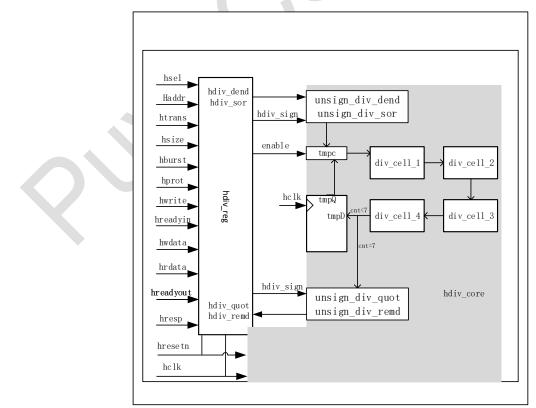

| 30. | Hare   | dware divider (HDIV)                                  | 457 |

| 3   | 0.1.   | Introduction                                          | 457 |

| 3   | 0.2.   | Main features                                         | 457 |

| 3   | 0.3.   | Functional overview                                   | 457 |

|     | 30.3.1 | . Overview                                            | 457 |

|     | 30.3.2 | Operation Process                                     | 458 |

| 3   | 0.4.   | HDIV register                                         |     |

|     | 30.4.1 | 5 ( = )                                               |     |

|     | 30.4.2 | <b>3</b> ( <b>1 )</b>                                 |     |

|     | 30.4.3 |                                                       |     |

|     | 30.4.4 | <b>5</b> ( <b>1</b> <i>i</i>                          |     |

|     | 30.4.5 | 5 5 ( <u> </u>                                        |     |

|     | 30.4.6 | 5 ( _ /                                               |     |

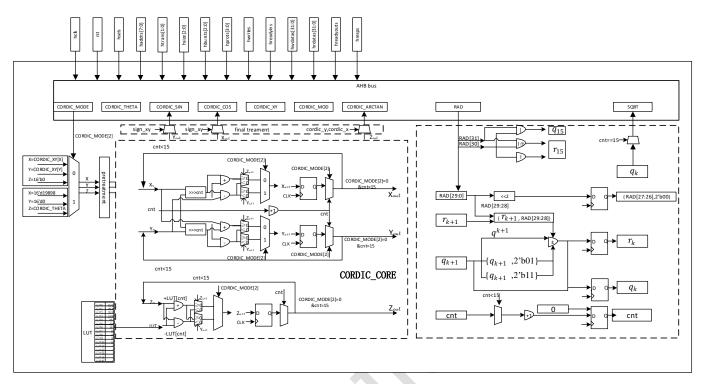

| 31. | Digi   | ital co-processing                                    |     |

| 3   | 1.1.   | Overview                                              |     |

| 3   | 1.2.   | Main features                                         |     |

| 3   | 1.3.   | Functional overview                                   |     |

|     | 31.3.1 | 5                                                     |     |

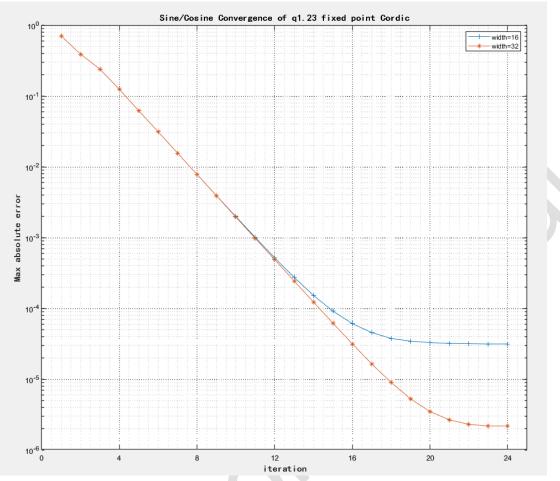

|     | 31.3.2 |                                                       |     |

|     | 31.3.3 | . Square root operation                               | 468 |

|     | 31.3.4 |                                                       |     |

| 3   | 1.4.   | Register                                              | 469 |

|     | 31.4.1 | . Cordic control register (CORIC _ CR)                | 469 |

|     | 31.4.2 | . SIN/COS input theta register (CORDIC _ theta)       | 470 |

|     | 31.4.3 | CORDIC _ SIN Result register (CORDIC _ SIN)           | 471 |

|     | 31.4.4 | CORDIC _ COS Result register (CORDIC _ COS)           | 471 |

|     | 31.4.5 | . Arctan input coordinate register (CORDIC _ X)       | 472 |

|     | 31.4.6 | Arctan input coordinate register (CORDIC _ Y)         | 472 |

|     | 31.4.7 | . CORDIC Mod result register (CORDIC _ MOD)           | 472 |

|     | 31.4.8 | ARCTAN result register (CORDIC _ ARCTAN)              | 473 |

|     | 31.4.9 | . Square root register (DSP _ RAD)                    | 473 |

|     | 31.4.1 | 0. SQRT results or registers (DSP _ SQRT)             | 473 |

|     | 31.4.1 | 1. Status register (CORIC _ SR)                       | 474 |

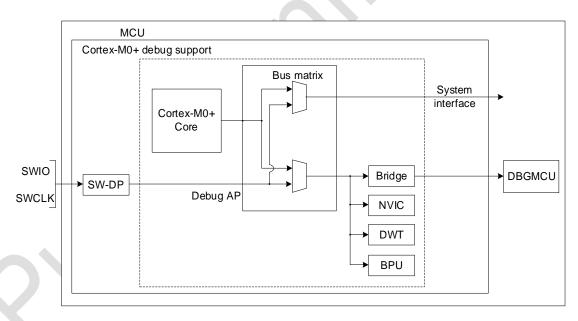

| 32. | Deb    | oug support (DBG)                                     | 475 |

| 3   | 2.1.   | Overview                                              | 475 |

| 3   | 2.2.   | Pinout and debug port pins                            | 475 |

|     | 32.2.1 | . SWD port                                            | 475 |

| 32.2.2.  | Flexible SWJ-DP pin assignment                         | 476 |

|----------|--------------------------------------------------------|-----|

| 32.2.3.  | Internal pull-up & pull-down on SWD pins               | 476 |

| 32.3.    | ID codes and locking mechanism                         | 476 |

| 32.4.    | SWD port                                               | 476 |

| 32.4.1.  | SWD protocol introduction                              | 476 |

| 32.4.2.  | SWD protocol introduction                              | 476 |

| 32.4.3.  | SW-DP state machine (reset, idle states, ID code)      | 477 |

| 32.4.4.  | DP and AP read/write accesses                          | 477 |

| 32.4.5.  | SW-DP registers                                        | 478 |

| 32.4.6.  | SW-AP registers                                        | 478 |

| 32.5.    | Core debug                                             |     |

| 32.6.    | BPU (Break Point Unit)                                 |     |

| 32.6.1.  | BPU functionality                                      |     |

| 32.7.    | DWT (Data Watchpoint)                                  |     |

| 32.7.1.  |                                                        |     |

| 32.7.2.  | - · · · F. · 3. ···· · · · · · · · · · · · · · ·       |     |

| 32.8.    | MCU debug component (DBG)                              |     |

| 32.8.1.  | Debug support for low-power modes                      | 479 |

| 32.8.2.  | Supports debugging of timers, watchdogs, bxCAN and I2C | 479 |

| 32.9.    | DBG register                                           |     |

| 32.9.1.  | DBG device ID code register (DBG _ IDCODE)             |     |

| 32.9.2.  | DBG configuration register (DBG_CR)                    |     |

| 32.9.3.  | DBG APB freeze register 1 (DBG _ APB _ FZ1)            | 481 |

| 32.9.4.  | DBG APB free register 2 (DBG _ APB _ FZ2)              | 481 |

| 33. Vers | sion history                                           |     |

## 1. List of abbreviations for registers

| Abbreviation              | Description                                                                                                                 |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Read/Write (RW)           | Software can read and write to this bit.                                                                                    |

| Read-only (R)             | Software can only read this bit.                                                                                            |

| Write-only (W)            | Software can only write to this bit.                                                                                        |

| Read/Clear Write0 (RC_W0) | Software can read as well as clear this bit by writing 0. Writing 1 has no effect on this bit.                              |

| Read/Clear Write1 (RC_W1) | Software can read as well as clear this bit by writing 1. Writing 0 has no effect on this bit.                              |

| Read/Clear Write1 (RC_W)  | The software can read and clear the bit by writing to the register. The value written to this bit is not important.         |

| Read/Clear by read (RC_R) | Software can read this bit. Reading this bit automatically clears it to 0. Writing this bit has no effect on the bit value. |

| Read/Set by Read (RS_R)   | Software can read this bit. Reading this bit automatically sets it to 1. Writing this bit has no effect on the bit value.   |

| Read/Set (RS)             | Software can read as well as set this bit by writing 1. Writing 0 has no effect on this bit.                                |

| Toggle (T)                | The software can toggle this bit by writing 1. Writing 0 has no effect.                                                     |

| Reserved (Res)            | Reserved bit, must be kept at reset value.                                                                                  |

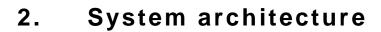

Figure 2-1 System architecture

## 3. Memory and bus architecture

## 3.1. System architecture

The system consists of:

- Two Masters

- Cortex-M0+

- General-purpose DMA

#### Three Slaves

- Internal SRAM

- Internal Flash memory

- AHB with AHB-APB bus bridge

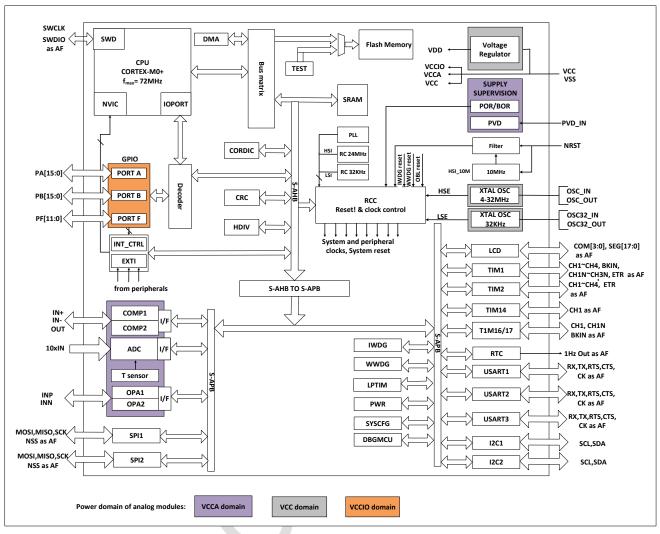

Figure 3-1 System architecture

#### System bus

This bus connects the system bus of the Cortex®-M0+ core to a Bus Matrix which manages the arbitration between the CPU and the DMA.

DMA bus

This bus connects the AHB master interface of the DMA to the Bus Matrix which manages the access of CPU and DMA to SRAM, Flash memory and AHB/APB peripherals.

Bus Matrix

The Bus Matrix manages the access arbitration between the core system bus and the DMA master bus. This arbitration uses the Round Robin algorithm. The BusMatrix is composed of up to two masters (CPU, DMA) and three slaves (FLASH memory, SRAM, and AHB-to-APB bridge).

■ AHB-to-APB bridge (APB)

The AHB to APB bridge provides full synchronous connections between the AHB and the APB bus and address mapping of the peripherals connected to this Bridge.

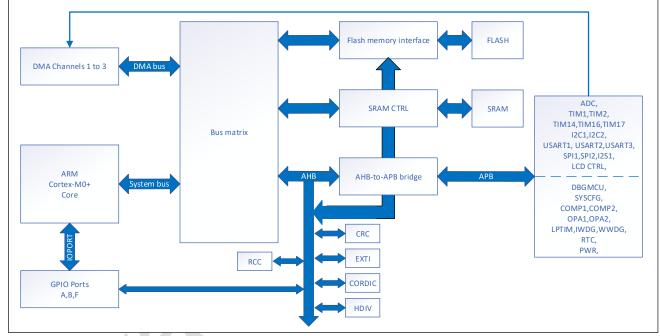

## 3.2. Memory organization

Program memory, data memory, registers and I/O ports are organized within the same linear 4 GB address space. The bytes are coded in memory in Little Endian format (the lowest numbered byte in a word is considered the word's least significant byte).

The addressable memory space is divided into 8 main blocks, of 512 MB each.

Figure 3-2 Memory map

| Туре | Boundary Address        | Size      | Memory Area           | Description                  |

|------|-------------------------|-----------|-----------------------|------------------------------|

| SRAM | 0x2000 2000-0x3FFF FFFF | -         | Reserved              | -                            |

| SKAW | 0x2000 0000-0x2000 1FFF | 8 KB      | SRAM                  | -                            |

|      | 0x1FFF 1000-0x1FFF FFFF | 4 KB      | Reserved              | -                            |

|      | 0x1FFF 0F80-0x1FFF 0FFF | 128 Bytes | Factory config. bytes | -                            |

|      | 0x1FFF 0F00-0x1FFF 0F7F | 128 Bytes | Factory config. bytes | Store HSI triming data       |

|      | 0x1FFF 0E80-0x1FFF 0EFF | 128 Bytes | Option bytes          | Software and hardware option |

|      | 0x1FFF 0E00-0x1FFF 0E7F | 128 Bytes | UID                   | Unique ID                    |

| Code | 0x1FFF 0D80-0x1FFF 0DFF | 128 Bytes | Reserved              | -                            |

| Code | 0x1FFF 0D00-0x1FFF 0D7F | 128 Bytes | User OTP Data         | User area                    |

|      | 0x1FFF 0000-0x1FFF 0CFF | 3.25 KB   | System memory         | deposit boot loader          |

|      | 0x0801 0000-0x1FFE FFFF | -         | Reserved              | -                            |

|      | 0x0800 0000-0x0800 FFFF | 64 KB     | Main flash memory     | -                            |

|      | 0x0001 0000-0x07FF FFFF | -         | Reserved              | -                            |

|      | 0x0000 0000-0x0000 FFFF | 64 KB     | Depending on the Boot | -                            |

Table 3-1 Memory Address

1. The address is marked as Reserved, which cannot be written and read as 0.

#### Table 3-2 Peripheral register address

| Bus    | Boundary Address        | Size | Peripheral |

|--------|-------------------------|------|------------|

|        | 0xE000 000-0xE00F FFFF  | 1 MB | M0+        |

|        | 0x5000 1800-0x5FFF FFFF | -    | Reserved   |

|        | 0x5000 1400-0x5000 17FF | 1 KB | GPIOF      |

|        | 0x5000 1000-0x5000 13FF | -    | Reserved   |

| IOPORT | 0x5000 0C00-0x5000 0FFF | -    | Reserved   |

|        | 0x5000 0800-0x5000 0BFF | -    | Reserved   |

|        | 0x5000 0400-0x5000 07FF | 1 KB | GPIOB      |

|        | 0x5000 0000-0x5000 03FF | 1 KB | GPIOA      |

|        | 0x4002 4000-0x4FFF FFFF | -    | Reserved   |

|        | 0x4002 3C00-0x4002 3FFF | -    | Reserved   |

|        | 0x4002 3800-0x4002 3BFF | 1 KB | HDIV       |

|        | 0x4002 3400-0x4002 37FF | 1 KB | CORDIC     |

|        | 0x4002 3000-0x4002 33FF | 1 KB | CRC        |

|        | 0x4002 2400-0x4002 2FFF | -    | Reserved   |

| АНВ    | 0x4002 2000-0x4002 23FF | 1 KB | Flash      |

|        | 0x4002 1C00-0x4002 1FFF | -    | Reserved   |

|        | 0x4002 1800-0x4002 1BFF | 1 KB | EXTI       |

|        | 0x4002 1400-0x4002 17FF | -    | Reserved   |

|        | 0x4002 1000-0x4002 13FF | 1 KB | RCC        |

|        | 0x4002 0400-0x4002 0FFF | -    | Reserved   |

|        | 0x4002 0000-0x4002 03FF | 1 KB | DMA        |

| Bus | Boundary Address        | Size | Peripheral      |

|-----|-------------------------|------|-----------------|

|     | 0x4001 5C00-0x4001 FFFF | -    | Reserved        |

|     | 0x4001 5800-0x4001 5BFF | 1 KB | DBG             |

|     | 0x4001 4C00-0x4001 57FF | -    | Reserved        |

|     | 0x4001 4800-0x4001 4BFF | 1 KB | TIM17           |

|     | 0x4001 4400-0x4001 47FF | 1 KB | TIM16           |

|     | 0x4001 3C00-0x4001 43FF | -    | Reserved        |

|     | 0x4001 3800-0x4001 3BFF | 1 KB | USART1          |

|     | 0x4001 3400-0x4001 37FF | -    | Reserved        |

|     | 0x4001 3000-0x4001 33FF | 1 KB | SPI1            |

|     | 0x4001 2C00-0x4001 2FFF | 1 KB | TIM1            |

|     | 0x4001 2800-0x4001 2BFF | -    | Reserved        |

|     | 0x4001 2400-0x4001 27FF | 1KB  | ADC             |

|     | 0x4001 0400-0x4001 23FF | -    | Reserved        |

|     | 0x4001 0300-0x4001 03FF |      | ОРА             |

|     | 0x4001 0200-0x4001 02FF | 1KB  | COMP1 and COMP2 |

|     | 0x4001 0000-0x4001 01FF |      | SYSCFG          |

|     | 0x4000 B400-0x4000 FFFF | -    | Reserved        |

|     | 0x4000 B000-0x4000 B3FF | -    | Reserved        |

| APB | 0x4000 8400-0x4000 AFFF | -    | Reserved        |

| AFD | 0x4000 8000-0x4000 83FF | -    | Reserved        |

|     | 0x4000 7C00-0x4000 7FF  | 1 KB | LPTIM           |

|     | 0x4000 7400-0x4000 7BFF | -    | Reserved        |

|     | 0x4000 7000-0x4000 73FF | 1 KB | PWR             |

|     | 0x4000 5C00-0x4000 6FFF | -    | Reserved        |

|     | 0x4000 5800-0x4000 5BFF | 1 KB | I2C2            |

|     | 0x4000 5400-0x4000 57FF | 1 KB | I2C1            |

|     | 0x4000 4C00-0x4000 53FF | -    | Reserved        |

|     | 0x4000 4800-0x4000 4BFF | 1 KB | USART3          |

|     | 0x4000 4400-0x4000 47FF | 1 KB | USART2          |

|     | 0x4000 3C00-0x4000 43FF | -    | Reserved        |

|     | 0x4000 3800-0x4000 3BFF | 1 KB | SPI2            |

|     | 0x4000 3400-0x4000 37FF | -    | Reserved        |

|     | 0x4000 3000-0x4000 33FF | 1 KB | IWDG            |

|     | 0x4000 2C00-0x4000 2FFF | 1 KB | WWDG            |

|     | 0x4000 2800-0x4000 2BFF | 1 KB | RTC             |

|     | 0x4000 2400-0x4000 27FF | 1 KB | LCD             |

|     | 0x4000 2000-0x4000 23FF | 1 KB | TIM14           |

|     | 0x4000 1800-0x4000 1FFF | -    | Reserved        |

| Bus | Boundary Address        | Size | Peripheral |

|-----|-------------------------|------|------------|

|     | 0x4000 1400-0x4000 17FF | -    | Reserved   |

|     | 0x4000 1000-0x4000 13FF | -    | Reserved   |

|     | 0x4000 0800-0x4000 13FF | -    | Reserved   |

|     | 0x4000 0400-0x4000 07FF | -    | Reserved   |

|     | 0x4000 0000-0x4000 03FF | 1 KB | TIM2       |

## 3.3. Embedded SRAM

PYF031 series feature 8 KB SRAM. It is accessed by half-word (16 bits) or word (32 bits).

The size of the SRAM can be set to 8 KB/6 KB/4 KB/2 KB by option byte to match the configurable flash size (When set to less than 8 KB, the software will generate a HardFault for reading and writing operations in the space outside the set range).

## 3.4. Flash memory

The Flash memory is composed of two distinct physical areas:

- The Main flash area: 64 KB, consisting of application and user data, Can be defined as 64 KB/48 KB/32 KB/16 KB depending on different products, and is used to store user programs and user data. When set to less than 64 KB capacity, software access to space outside the set range produces a HardFault.

- 4 KB of Information area:

- Factory config. bytes 0, 128 Bytes, used to store

- HSI frequency selection value and corresponding Trimming value

- Configuration parameter values of erase and write time corresponding to different frequencies of HSI

- Factory config. Bytes 1: 128 Bytes for storing:

- Power-on verification code reading

- UID: 128 Bytes, used to store the UID

- Option byte: 128 Bytes, used to store configuration values for hardware and storage protection

- User OTP Memory: 128 Bytes, used to store user data

Flash interface realizes instruction reading and data access based on AHB protocol, and it also realizes basic write/erase operations of flash through registers.

### 3.5. Boot modes

At startup, the nBOOT0 pin and nBOOT1 (stored in Option bytes) are used to select one of the three boot options in the following table:

| Boot mode of | onfiguration | Mode                    |  |

|--------------|--------------|-------------------------|--|

| nBOOT1 bit   | BOOT0 pin    | Mode                    |  |

| Х            | 0            | Boot from Main flash    |  |

| 1            | 1            | Boot from System memory |  |

| 0            | 1            | Boot from SRAM          |  |

#### Table 3-3 Boot configuration

After this startup delay has elapsed, the CPU fetches the top-of-stack value from address 0x0000 0000, then starts code execution from the boot memory at 0x0000 0004. Depending on the selected boot mode, Main flash memory, system memory or SRAM is accessible as follows:

- Boot from main flash: the main Flash memory is aliased in the boot memory space (0x0000 0000), but still accessible from its original memory space (0x0800 0000). In other words, the Flash memory contents can be accessed starting from address 0x0000 0000 or 0x0800 0000.

- Boot from system memory: The system memory is aliased in the boot memory space (0x0000 0000), but it is still accessible from its original memory space (0x1FFF 0000).

- Boot from SRAM: the SRAM is aliased in the boot memory space (0x0000 0000), but it is still accessible from its original memory space (0x2000 0000).

#### 3.5.1. Memory physical mapping

If the Boot mode is selected, the application software can modify the memory that is accessible in the program space. This modification is determined by the MEM \_ MODE bit selection of SYSCFG configuration register 1 (SYSCFG \_ CFGR1).

#### 3.5.2. Embedded bootstrapper

The Boot loader is written during the chip production phase and stored in the system memory. It is used to re-write to flash memory using the following serial interface:

■ USART for PA14/PA15 or PA9/PA10 or PA2/PA3

## 4. Embedded Flash memory

## 4.1. Main features of flash memory

- Main flash block: maximum 64 KB (16k x 32 bits)

- Information block: 4 KB (1k x 32 bits)

- Page size: 128 Bytes

- Sector size: 4 KB

Flash memory interface features:

- Flash memory read, write and erase

- Write protection

- Read protection

### 4.2. Flash memory functional description

#### 4.2.1. Flash memory organization

The Flash memory is organized as 32-bit wide memory cells that can be used for storing both code and data constants. The Page size is 128 Bytes and the Sector size is 4 KB.

Functionally, Flash memory is divided into Main flash and information flash. The former has a capacity of 64 KB and the latter has a capacity of 8 KB.

The Page erase operation can be applied to the Main flash.

If write protection is set, Mass erase can be applied to Main flash.

| Block Sector Page Base address Size |              |              |                         |          |  |  |

|-------------------------------------|--------------|--------------|-------------------------|----------|--|--|

| BIOCK                               | Sector       | Page         | Base address            | Size     |  |  |

|                                     | Sector 0     | Page 0-31    | 0x0800 0000-0x0800 0FFF | 4KB      |  |  |

|                                     | Sector 1     | Page 32-63   | 0x0800 1000-0x0800 1FFF | 4KB      |  |  |

| Main memory                         | Sector 2     | Page 64-95   | 0x0800 2000-0x0800 2FFF | 4KB      |  |  |

| Main memory                         |              |              |                         |          |  |  |

|                                     | Sector 14    | Page 448-479 | 0x0800 E000-0x0800 EFFF | 4KB      |  |  |

|                                     | Sector 15    | Page 480-511 | 0x0800 F000-0x0800 FFFF | 4KB      |  |  |

| System memory                       | ystem memory |              | 0x1FFF 0000-0x1FFF 0CFF | 3.25 KB  |  |  |

| User Data                           |              | Page 26      | 0x1FFF 0D00-0x1FFF 0D7F | 128bytes |  |  |

| Reserved                            |              | Page 27      | 0x1FFF 0D80-0x1FFF 0DFF | 128bytes |  |  |

| UID                                 | Sector 16    | Page 28      | 0x1FFF 0E00-0x1FFF 0E7F | 128bytes |  |  |

| Option bytes                        |              | Page 29      | 0x1FFF 0E80-0x1FFF 0EFF | 128bytes |  |  |

| Factory config 0                    |              | Page 30      | 0x1FFF 0F00-0x1FFF 0F7F | 128bytes |  |  |

| Factory config 1                    |              | Page 31      | 0x1FFF 0F80-0x1FFF 0FFF | 128bytes |  |  |

#### Table 4-1Flash structure and boundary address

### 4.2.2. Flash read operation and access latency

The embedded Flash module can be addressed directly, as a common memory space. Through the special read control timing, the contents of the Flash memory can be read.

Both fetching and data access are carried out through the AHB bus. Read accesses can be performed through the Latency of the FLASH\_ACR register, that is, number of wait states for a correct read operation is zero or one.

flash \_ ACR.0 (LATENCY) bit, when it is 0, the wait state of the flash read operation is not increased; When it is 1, the flash read operation adds 1 waiting state; When it is 2, the flash read operation adds 3 wait states. This mechanism is specially designed to match the high-speed system clock and the relatively low Flash read speed.

#### 4.2.3. Flash program and erase operations

The Flash memory can be programmed using in-circuit programming (ICP) or in-application programming (IAP).

ICP: used to update the entire contents of the Flash memory, using the SWD protocol or the boot loader to load the user application into the microcontroller. ICP provides fast and efficient design iterations and eliminates unnecessary packet processing or socketing.

IAP: using any communication interface supported by the microcontroller to download programming data into Flash memory. IAP allows the user to re-program the Flash memory while the application is running. Nevertheless, part of the application has to have been previously programmed in the Flash memory using ICP.

If a reset occurs when a Flash write or erase operation is performed, the contents of the Flash memory are not protected.

During a write or erase operation, any operation to read the flash will delay the bus. The read operation will proceed correctly once the program/erase operation has completed. This means that code or data fetches cannot be made while a program/erase operation is ongoing.

For write and erase operations, the HSI must be turned on (the software configures the corresponding parameters according to the HSI frequency to the erase and write time control register).

Write and erase operations can be implemented through the registers related to the following flash control interface:

- Acess control register (FLASH \_ ACR)

- KEY register (FLASH \_ KEYR)

- Option byte key register (FLASH \_ OPTKEYR)

- Flash status register (FLASH \_ SR)

- Flash control register (FLASH \_ CR)

- Flash option register (FLASH \_ OPTR)

- Flash special area address register (FLASH \_ SDKR)

- Flash write protection resister (FLASH \_ WRPR)

- Flash sleep time config register (FLASH \_ STCR)

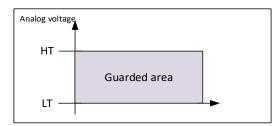

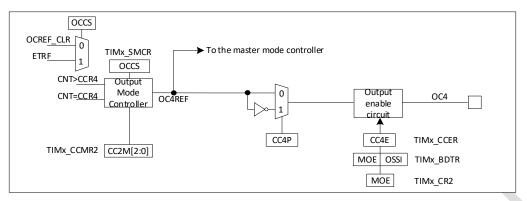

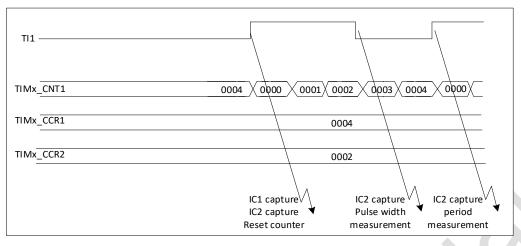

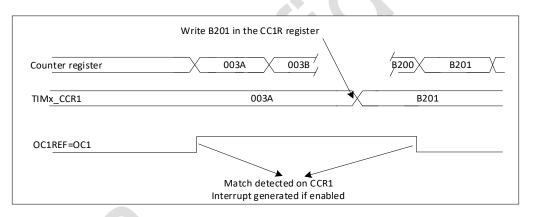

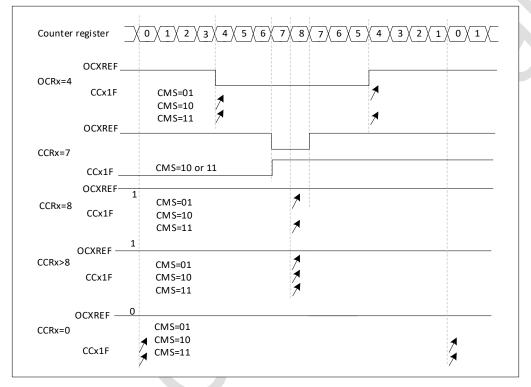

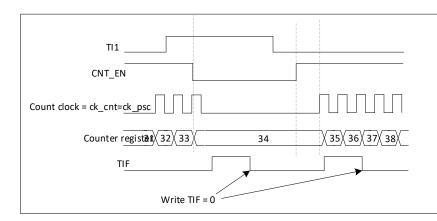

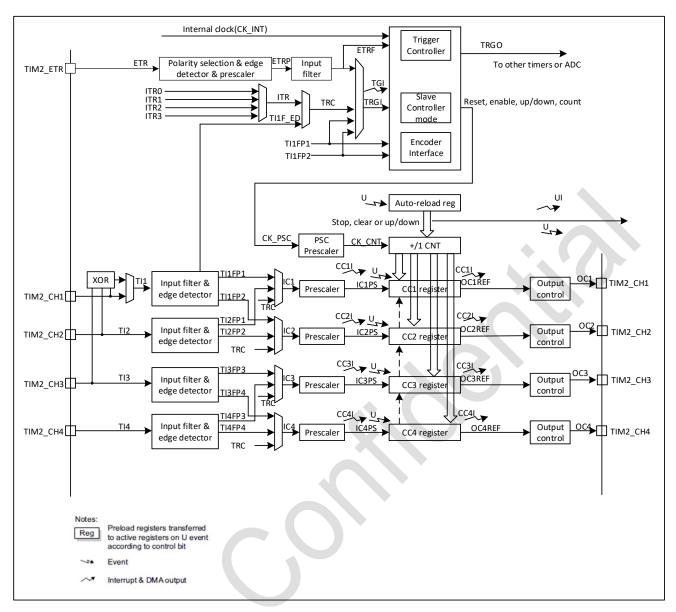

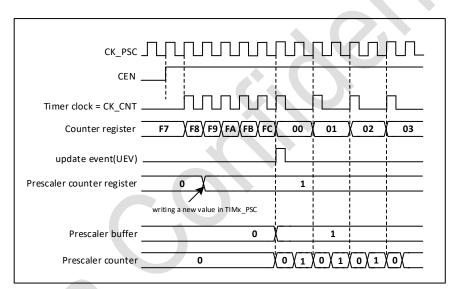

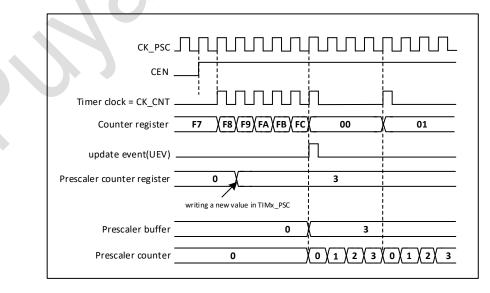

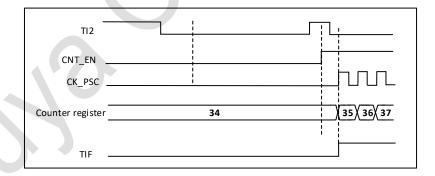

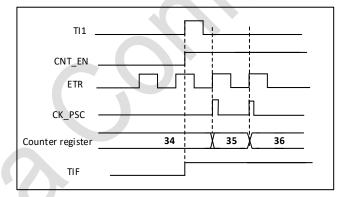

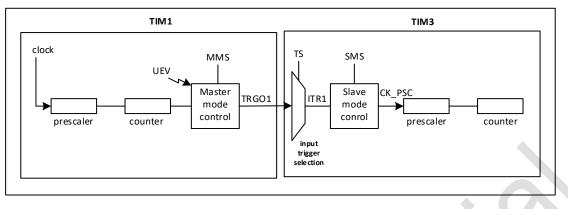

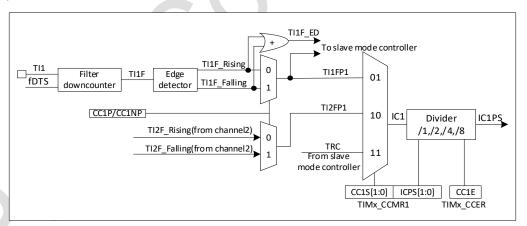

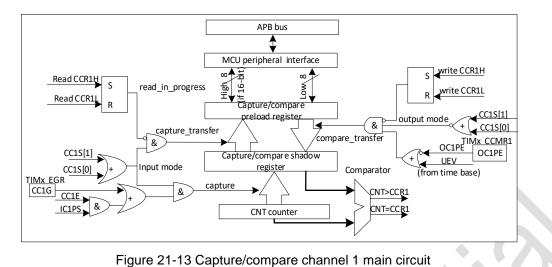

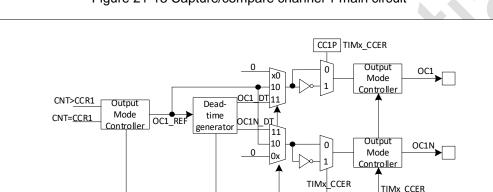

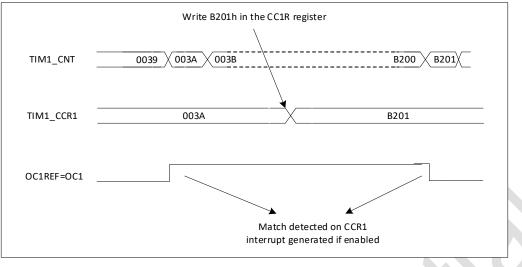

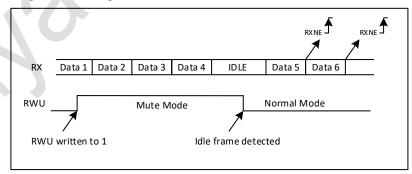

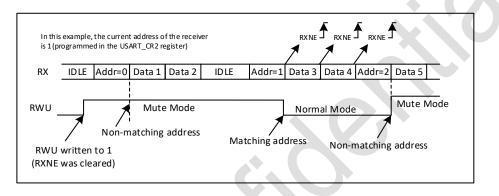

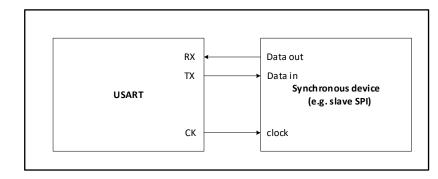

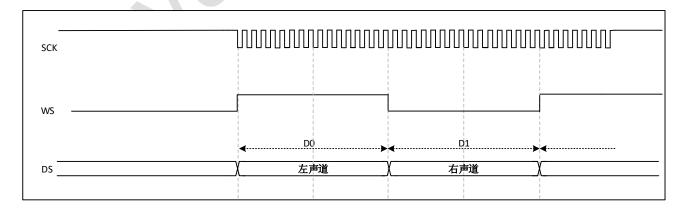

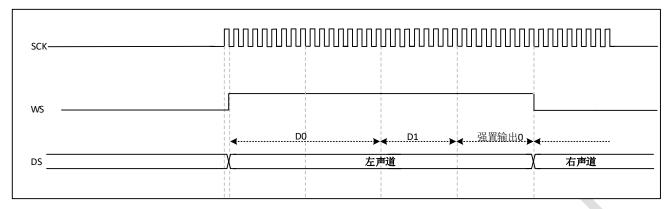

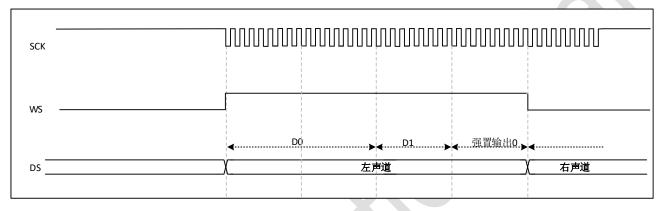

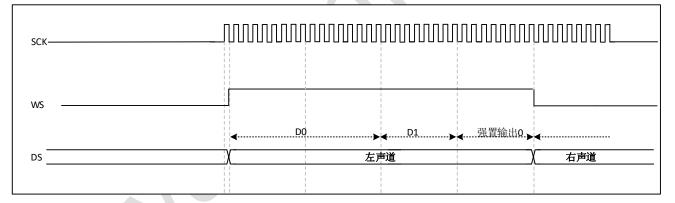

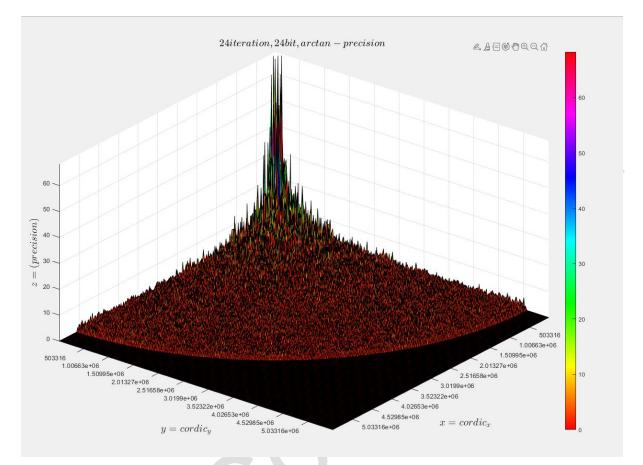

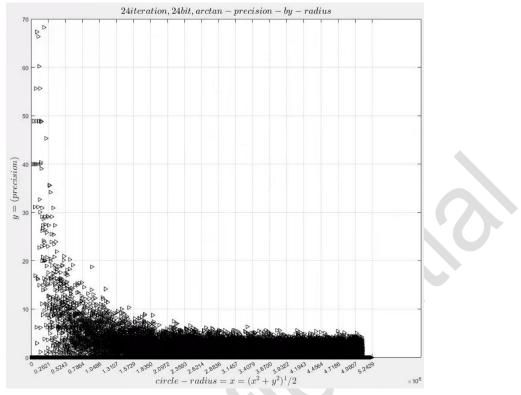

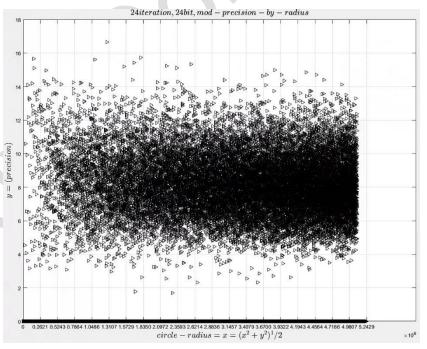

- Flash TS0 register(FLASH\_TS0)